# Electrical Measurement of Local Stress and Lateral Diffusion Near Source/Drain Extension Corner of Uniaxially Stressed n-MOSFETs

Chen-Yu Hsieh, Student Member, IEEE, and Ming-Jer Chen, Senior Member, IEEE

Abstract—On a 1.27-nm gate oxide n-MOSFET that undergoes longitudinal stress via a layout technique, subthreshold current is measured as a function of the gate edge to shallow-trench isolation (STI) spacing and is transformed via bandgap shift into the source/drain extension corner stress. The extracted local stress is quantitatively comparable with those of the channel as created by the gate direct tunneling measurement in inversion, the mobility measurement, and the threshold voltage measurement. In addition, its dependencies on the gate edge to STI spacing confirm the validity of the layout technique in controlling the corner or channel stress. The gate edge direct tunneling (EDT) measurement in accumulation straightforwardly leads to the quantified gateto-source/drain-extension overlap length. Particularly, a retarded diffusion length of 1.1 nm for a stress change of -320 MPa and the resulting strain-induced activation energy both are in satisfactory agreement with those of the process simulation. A physically oriented analytic model is, therefore, reached, expressing the lateral diffusion as a function of the corner stress.

*Index Terms*—Dopant diffusion, mechanical stress, MOSFET, piezoresistance, shallow-trench isolation (STI), strain, tunneling.

# I. INTRODUCTION

ECHANICAL stress has been widely recognized to be one of the key issues in the area of highly scaled MOSFETs. So far, there have been two distinct directions concerning the significance of the mechanical stress. On the one hand, the mechanical stress experienced during the manufacturing process can enhance or retard the dopant diffusion, thereby influencing the final doping profile of the device. There have been significant studies with emphasis on the material aspect covering a wide range of experimental findings and confirmations [1]-[8], as well as the atomistic calculations and physical models [1], [9]-[12]. Extension to the actual devices has been achieved by means of the sophisticated device/processcoupled simulation, namely the technology computer-aided design (TCAD) [10], [13], [14]. On the other hand, the presence of the mechanical stress can also alter the band structure of the formed device, which, in turn, can significantly affect properties such as mobility [15]–[17], hot carrier immunity [18], threshold

Manuscript received August 27, 2007; revised November 28, 2007. This work was supported by the National Science Council of Taiwan under Contract NSC 95-2221-E-009-295-MY3. The review of this paper was arranged by Editor H. Jaouen.

The authors are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 30010, Taiwan, R.O.C. (e-mail: cyhsieh. ee93g@nctu.edu.tw; chenmj@faculty.nctu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2007.915050

voltage [19], and gate direct tunneling [20]–[23]. Besides the aforementioned TCAD technique [10], [13], [14], there have been several methods applied on the formed devices with which the magnitude of the underlying stress and its status both can be determined: 1) wafer bending jig [24]; 2) stress/strain simulation and modeling [25]; 3) Raman spectroscopy [26]; and 4) gate direct tunneling [23].

Indeed, the ability of tracing the electrical measurements on the formed devices back to the stress-related dopant diffusion in the manufacturing process is essential. Traditionally, this was done with the TCAD method [10], [13], [14], as mentioned before. In this paper, we present the *electrical* approach to the local mechanical stress around the source/drain extension corner of uniaxially stressed n-MOSFETs, which can straightforwardly determine the underlying lateral diffusion. The validity of the proposed method will be addressed in detail.

## II. DEVICE UNDER STUDY

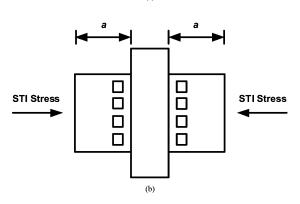

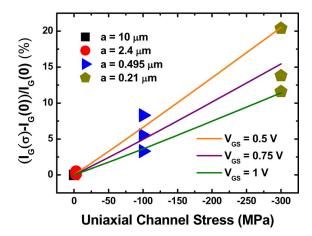

The test device was an n<sup>+</sup> polysilicon gate n-MOSFET as fabricated in a state-of-the-art manufacturing process. The device process flow is depicted in Fig. 1. Also plotted in the figure is the schematic topside view of the test device. Three key process parameters were obtained by capacitance-voltage (C-V)fitting:  $n^+$  polysilicon doping concentration =  $1 \times 10^{20}$  cm<sup>-3</sup>, gate oxide thickness = 1.27 nm, and substrate doping concentration =  $4 \times 10^{17}$  cm<sup>-3</sup>. In this process, the shallow-trench isolation (STI)-induced compressive stress was applied. The gate length along the  $\langle 1 \ 1 \ 0 \rangle$  direction is 1  $\mu$ m large enough that the following effects can be effectively eliminated: external series resistance and short-channel or drain-induced barrier lowering (DIBL). The gate width has a large value of 10  $\mu$ m, indicating that the transverse strain is relatively negligible. A layout technique was utilized to produce a variety of stress in terms of the gate edge to STI sidewall spacing, designated as a, with four values of 10, 2.4, 0.495, and 0.21  $\mu$ m. A decrease in a means increased magnitude of longitudinal stress. Considerable number of contacts were formed on the source/drain diffusion along the gate width direction, far away from the STI in the  $\langle 1 \ 1 \ 0 \rangle$  direction. The spacing between the diffusion contact and the gate edge is fixed in this paper. With the source, drain, and substrate all tied to ground, the measured valence-band electron tunneling current in inversion (for the gate voltage  $V_G$ larger than the threshold voltage  $V_{\rm th}$ ) or equivalently the substrate hole current was found to be unchanged, regardless of the stress. This indicates that the gate oxide thickness under study remains constant.

Fig. 1. (a) Device formation process flow. (b) Schematic topside view of the device. The gate edge to STI sidewall spacing *a* is highlighted. The stress condition is compressive due to the lower thermal expansion rate of STI oxide compared to silicon.

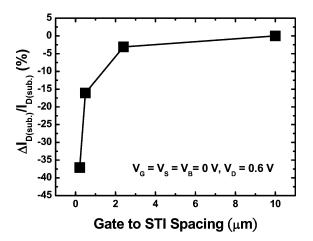

Fig. 2. Measured subthreshold current change versus gate-to-STI spacing.

### III. CORNER STRESS EXTRACTION AND VALIDATION

Measurement of the subthreshold current is adopted to quantify the mechanical stress around the source/drain extension diffusion corner. The measured subthreshold current change with respect to the reference device, namely  $a=10~\mu \mathrm{m}$ , is shown in Fig. 2, revealing a decreasing trend with decreasing gate-to-STI spacing. Since the mobility in depletion ( $V_G < V_{\mathrm{th}}$ ) is primarily due to Coulomb scattering rather than phonon scattering, and hence is independent of stress, the subthreshold current must be proportional to  $n_i^2$  only, where  $n_i$  is the intrin-

Fig. 3. Extracted bandgap change and source/drain extension corner stress versus gate-to-STI spacing.

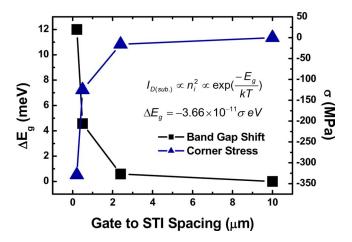

Fig. 4. Experimental gate current change percentage versus uniaxial channel stress with both gate-to-STI spacing and gate voltage as parameters.

sic concentration. As a result, the change of the subthreshold current can be transformed into the bandgap change  $\Delta E_g$ , as shown in Fig. 3. By means of a well-known relationship of  $\Delta E_g = -3.66 \times 10^{-11} \sigma$  eV [19], the extracted  $\Delta E_g$  further produces the source/drain extension corner stress of -20, -125, and -320 MPa for a of 2.4, 0.495, and 0.21  $\mu$ m, respectively, as illustrated in Fig. 3.

The extracted corner stress is found to be comparable with those of the channel as created by other electrical measurements on the same device. First, by incorporating the stress dependencies of quantized energies [22], [23], [27]–[29] into a triangular potential method [30] in the channel, a Wentzel–Kramers–Brillouin (WKB) tunneling approach [31] was adopted to quantify the conduction-band electron direct tunneling current. As a consequence, the uniaxial channel stress of 0,  $\sim$ 0, -100, and -300 MPa was extracted for gate-to-STI spacing of 10, 2.4, 0.495, and 0.21  $\mu$ m, respectively, each of which can reproduce experimental gate direct tunneling current versus gate voltage characteristics. The detailed extraction process can be found elsewhere [23]. The corresponding gate current change is plotted in Fig. 4 versus extracted channel stress with gate voltage as a parameter. It was found that the twofold subband  $\Delta_2$

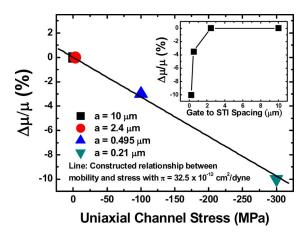

Fig. 5. Measured mobility change percentage versus extracted stress. The inset demonstrates the mobility variation versus gate-to-STI spacing.

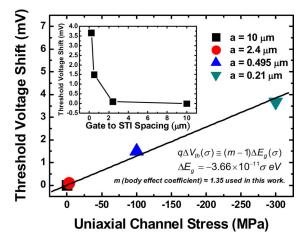

Fig. 6. Measured threshold voltage shift versus extracted stress. The inset shows the threshold voltage shift versus gate-to-STI spacing.

lies a few kT below the fourfold subband  $\Delta_4$  at high gate voltages, and therefore electrons primarily populate  $\Delta_2$ , whereas for low gate voltages, electrons populate both  $\Delta_2$  and  $\Delta_4$ . Hence, at low gate voltages, stress gives rise to not only a change in the barrier height but also an increased population in  $\Delta_4$ . This effect becomes weakened for high gate voltages due to the dominating  $\Delta_2$  electrons. As a result, the gate current change due to the stress increases with decreasing gate voltage (refer to [22] for the detailed interpretations). Second, the mobility at  $V_D = 25$  mV was characterized. The measured mobility change percentage versus extracted stress is shown in Fig. 5. A straight line used to fit the data points yields the slope or piezoresistance coefficient of  $32.5 \times 10^{-12} \text{ dyne}^{-1} \text{ cm}^2$ , close to that  $(31.5 \times 10^{-12} \text{ dyne}^{-1} \text{ cm}^2)$  in the literature [32]. The inset depicts the corresponding mobility change as a function of the gate-edge-to-STI spacing. Third, the threshold voltage measurement was conducted at  $V_D=25$  mV. As shown in Fig. 6, the threshold voltage shift  $\Delta V_{\mathrm{th}}$  produces a straight line of its own. This line can be related to the body-effect coefficient m and the band offset  $\Delta E_g$  [19]:  $q\Delta V_{\rm th}(\sigma) \approx (m-1)\Delta E_g(\sigma)$ . The band offset term can further be linked to the strain  $\varepsilon$  [19]:  $\Delta E_g = -6.19\varepsilon = -3.66 \times 10^{-11} \sigma$  eV. The slope of the line in

Fig. 7. Extracted channel and corner stress, divided by that of the minimum *a*, versus the gate-to-STI spacing, along with fitting curves from [25].

Fig. 6 furnishes m = 1.35, which exactly falls within the cited range of 1.3–1.4 [19].

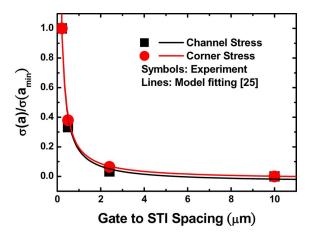

Finally, to testify to the validity of the layout technique, we quote the existing relationship between the effective stress and the gate-to-STI spacing, which was derived from the stress simulation [25]

$$\sigma(a) = \sigma(a_{\min}) \left( 1 + V_{m\sigma} \frac{a - a_{\min}}{a} \right) \tag{1}$$

where  $a_{\min}$  represents the minimum gate-to-STI spacing and  $V_{m\sigma}$  is the maximum  $\sigma(a)$  variation (i.e., when  $a\to\infty$ ) with respect to  $\sigma(a_{\min})$ . Evidently, as displayed in Fig. 7, the extracted channel stress and corner stress for a given gate-to-STI spacing are close to each other, indicating that the stress distribution beneath the gate oxide is considerably uniform. In addition, the corner stress follows the same trend as the channel counterpart. The resulting  $V_{m\sigma}$  values are comparable as well: -1.04 for the channel stress and -1.02 for the corner stress. Good fitting quality in both stress cases confirms the validity of the layout technique in *controlling* the stress there.

### IV. LATERAL DIFFUSION EXTRACTION AND CONFIRMATION

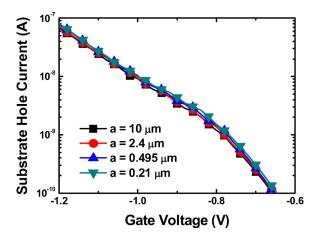

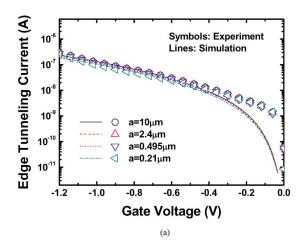

The electron direct tunneling from the accumulated polysilicon surface down to the underlying silicon was measured versus negatively biased gate voltage with the source, drain, and substrate all tied to the ground. It can be seen in Fig. 8 that the resulting substrate hole current, which essentially is equal to the electron gate-to-substrate tunneling current, increases with decreasing a. Such dependency reflects the increasing magnitude of lateral compressive stress in the polysilicon. The confirmative evidence of this origin is that for a given gate-to-STI spacing, the corner stress and channel stress both are comparable, and since the tunnel oxide is rather thin, the lateral compressive stress at the surface of the polysilicon is reasonably close to that of the underlying silicon. In contrast, the simultaneously measured source/drain or edge direct tunneling (EDT) current decreases with decreasing a, as shown in Fig. 9. To determine the underlying gate-to-source/drainextension overlap length where the EDT prevails, the existing

Fig. 8. Measured substrate hole current versus negative gate voltage.

Fig. 9. (a) Comparison of calculated and measured edge direct tunneling current versus negative gate voltage. (b) Band diagram drawn along  $\rm n^+$  polygate/  $\rm SiO_2/diffusion$  extension.

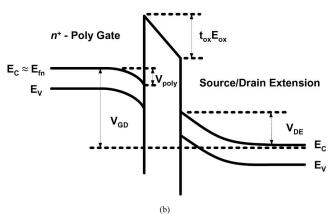

edge direct tunneling models [33]–[35] on the basis of the triangular potential approximation [30] can readily apply with some slight modifications such as incorporating stress dependencies of the subbands in the accumulated polysilicon surface. First of all, the oxide field  $E_{\rm ox}$  at the gate edge is determined through the following expression:

$$V_{\rm DG} - V_{\rm FB} = V_{\rm poly} + t_{\rm ox} E_{\rm ox} + V_{\rm DE}$$

(2)

where  $V_{\rm DG}$  is the applied source/drain-to-gate voltage,  $V_{\rm FB}$  is the flatband voltage,  $t_{\rm ox}$  is the gate oxide thickness, and  $V_{\rm poly}$  and  $V_{\rm DE}$  are the potential drops in the  $\rm n^+$  polysilicon and source/drain extension region, respectively. The accumulated electrons mainly populate in the first subband  $E_1$  due to the lowest quantized energy dominating. Then, relating the sheet charge density to the number of occupied subband states can establish the charge conservation relationship

$$q\left(E_{\rm fn} - E_1\right) \frac{\eta m_d}{\pi \hbar^2} = \varepsilon_{\rm ox} E_{\rm ox} = Q \tag{3}$$

where  $E_{\rm fn}$  is the quasi-Fermi level in  $\rm n^+$  polygate,  $\eta$  is the degeneracy factor, and Q is the available charge for tunnel process. The corresponding stress dependency of the quantized energy is well defined in the literature [22], [23], [27]–[29]

$$E_{1}(\sigma) = \left(\frac{9hq\varepsilon_{\text{ox}}E_{\text{ox}}}{16\varepsilon_{\text{Si}}\sqrt{2m_{z}}}\right)^{2/3} + \left(\Xi_{d} + \frac{\Xi_{u}}{3}\right)(S_{11} + 2S_{12})\sigma + \left(\frac{\Xi_{u}}{3}\right)(S_{12} - S_{11})\sigma$$

$$(4)$$

where the elastic compliance constants  $S_{11} = 7.68 \times 10^{-12}$  m<sup>2</sup>/N and  $S_{12} = -2.14 \times 10^{-12}$  m<sup>2</sup>/N. The hydrostatic and shear deformation potential constants  $\Xi_d = 1.13$  eV and  $\Xi_u = 9.16$  eV [19], close to those of [22], were cited here. With the aforementioned parameters as input, the lowest subband level with respect to the Fermi level can be quantified. Employing the lowest subband approximation to the accumulated n<sup>+</sup> polygate and the deep depletion approximation to the source/drain extension region, as drawn in Fig. 9(b), the following expressions can, therefore, be derived:

$$V_{\rm poly} \approx \frac{E_{\rm fn}}{a} = \varepsilon_{\rm ox} E_{\rm ox} \frac{\pi \hbar^2}{a^2 n m_d} + \frac{E_1}{a}$$

(5)

$$V_{\rm DE} = \frac{\varepsilon_{\rm ox}^2 E_{\rm ox}^2}{2q\varepsilon_{\rm Si} N_{\rm DE}} \tag{6}$$

where  $N_{\rm DE}$  is the dopant concentration of the source/drain extension. Here, the quantization effective masses  $m_z=0.98~m_0$  and  $m_d=0.19~m_0$ , and  $\eta=2$  were adopted to approximate the band structure for  $\langle 1~0~0 \rangle$  oriented polysilicon grain [31]. Then, it is a straightforward task to calculate the WKB tunneling probability, taking into account the corrections for reflections from the potential discontinuities [31]. Here, the electron effective mass in the oxide for the Franz-type dispersion relationship was used with  $m_{\rm ox}=0.61~m_0$ . The SiO<sub>2</sub>/Si interface barrier height in the absence of stress is 3.15 eV. Consequently, the edge electron direct tunneling current density can be calculated as a function of the stress  $\sigma$

$$I_{\rm EDT}(\sigma) = W L_{\rm TN} \frac{Q}{\tau_1(\sigma)}$$

(7)

where W is the channel width, and  $L_{\rm TN}$  is the gate-to-source/drain-extension overlap length. The tunneling lifetime in this equation can be connected with the transmission probability T:  $\tau_1(\sigma) = \pi \hbar/(T_1(\sigma)E_1(\sigma))$ .

Then, with known process parameters and published deformation potential constants [19] as input, the measured EDT was

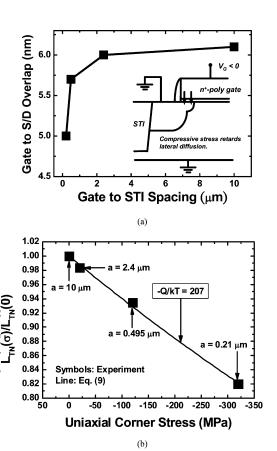

Fig. 10. (a) Extracted gate-to-source/drain extension overlap length versus gate-to-STI spacing. The decreasing trend with decreasing a can be related to the retarded lateral diffusion under the influence of the compressive stress. (b) Extracted (symbols) extension overlap length change versus corner stress. Also shown is a fitting line from (9).

reproduced well, as displayed in Fig. 9(a). Electron tunneling onto the forbidden silicon bandgap occurs in  $-0.1 \text{ V} < V_G <$ 0 V; however, an appreciable gate current was measured there. This indicates the existence of the oxide traps or interface states. Only at a more negatively biased gate voltage where the EDT dominates can the effect of the traps be alleviated. In addition, it was found experimentally that the gate edge direct tunneling current is several orders of magnitude larger than the gateto-substrate current, and hence is dominant over the gate voltage range of interest. The extracted gate-to-source/drain overlap  $L_{\rm TN}$  spans a range of 6.1, 6.0, 5.7, and 5.0 nm for a of 10, 2.4, 0.495, and 0.21  $\mu$ m, respectively, as demonstrated in Fig. 10(a). The  $L_{\rm TN}$  values are found to be comparable with those in the literature [33]-[35]. The shift of around 1.1 nm, caused by retarded dopant lateral diffusion for stress change from 0 to -320 MPa, is reasonable with respect to the process simulation [13]. In the cited work [13], a device/process-coupled simulation was carried out to produce the lateral doping profile from the source through the channel to the drain, with and without the strain dependencies. The resulting doping profiles reveal the retarded diffusion of about 1.8 nm as caused by a stress change from -10 to -500 MPa. It is, therefore, inferred that the extracted local stress and lateral diffusion shift are in satisfactory agreement with those of the process simulation published elsewhere [13].

Finally, it is noticed that the gate-to-source/drain-extension overlap length designated  $L_{\rm TN}$  is essentially proportional to the square root of the dopant diffusivity D. The stress-dependent dopant diffusivity can be expressed as [1], [4], [12]

$$D(\varepsilon) = D(0) \exp\left(\frac{-Q\varepsilon}{kT}\right) \tag{8}$$

where Q is the strain-induced activation energy and  $\varepsilon$  is the uniaxial strain.  $\varepsilon$  can be related to the uniaxial stress  $\sigma$ :  $\sigma = Y \varepsilon$ , where Y is the Young's modulus. Then, the effect of the stress on the extension overlap length can be derived

$$\frac{L_{\rm TN}(\sigma)}{L_{\rm TN}(0)} = \exp\left(\frac{-Q\sigma}{2kTY}\right). \tag{9}$$

The extracted extension overlap length is plotted in Fig. 10(b) versus the uniaxial corner stress. Fitting of the data yields a value of -Q/kT=207. Assuming a typical temperature of  $T=1300\,\mathrm{K}$  for the manufacturing process, the activation energy Q of  $-23.3\,\mathrm{eV}$  results, which is reasonable relative to those (-14 eV for arsenic and  $-30\,\mathrm{eV}$  for phosphorus) of the process simulation [13]. Therefore, a physically oriented analytic model is reached, expressing the lateral diffusion as a function of the corner stress.

### V. CONCLUSION

With the aid of the layout technique, the source/drain extension corner stress has been, for the first time, extracted by using the subthreshold current measurement, and has been compared with the channel stress obtained by the additional measurements on the gate direct tunneling in inversion, mobility, and threshold voltage. The validity of the layout technique has been confirmed as well. With known process parameters and published deformation potential constants as input, fitting of the gate edge direct tunneling data has led to the value of the underlying lateral diffusion. The retarded lateral diffusion length and the strain-induced activation energy both have been quantitatively consistent with those of the process simulation. A physically oriented analytic model has been reached, expressing the lateral diffusion as a function of the corner stress.

### ACKNOWLEDGMENT

The authors would like to thank Dr. Y.-M. Sheu for helpful discussions.

### REFERENCES

- [1] M. J. Aziz, Y. Zhao, H. J Gossmann, S. Mitha, S. P. Smith, and D. Schiferl, "Pressure and stress effects on the diffusion of B and Sb in Si and Si-Ge alloys," *Phys. Rev. B, Condens. Matter*, vol. 73, pp. 054101-1–054101-20, Feb. 2006.

- [2] N. Moriya, L. C. Feldman, H. S. Luftman, C. A. King, J. Bevk, and B. Freer, "Boron diffusion in strained Si<sub>1-x</sub> Ge<sub>x</sub>," *Phys. Rev. Lett.*, vol. 71, pp. 883–886, Aug. 1993.

- [3] P. Kuo, J. L. Hoyt, J. F. Gibbons, J. E. Turner, R. D. Jacowitz, and T. I. Kamins, "Comparison of boron diffusion in Si and strained Si<sub>1-x</sub>Ge<sub>x</sub>," Appl. Phys. Lett., vol. 62, pp. 612–614, Feb. 1993.

- [4] N. E. B. Cowern, P. C. Zalm, P. Van Der Sluis, D. J. Gravesteijn, and W. B. de Boer, "Diffusion in strained Si(Ge)," *Phys. Rev. Lett.*, vol. 72, pp. 2585–2588, Apr. 1994.

- [5] F. H. Baumann, J. H. Huang, J. A. Rentschler, T. Y. Chang, and A. Ourmazd, "Multilayers as microlabs for point defects: Effect of strain

- on diffusion in semiconductors," *Phys. Rev. Lett.*, vol. 73, pp. 448–451, Jul. 1994.

- [6] P. Kuo, J. L. Hoyt, J. F. Gibbons, J. E. Turner, and D. Lefforge, "Effects of strain on boron diffusion in Si and Si<sub>1-x</sub> Ge<sub>x</sub>," *Appl. Phys. Lett.*, vol. 66, pp. 580–582, Jan. 1995.

- [7] P. Kringhoj, A. N. Larsen, and S. Y. Shirayev, "Diffusion of Sb in strained and relaxed Si and SiGe," *Phys. Rev. Lett.*, vol. 76, pp. 3372–3375, Apr. 1996.

- [8] N. R. Zangenberg, J. Fage-Pedersen, J. L. Hansen, and A. N. Larsen, "Boron and phosphorus diffusion in strained and relaxed Si and SiGe," *J. Appl. Phys.*, vol. 94, pp. 3883–3890, Sep. 2003.

- [9] M. S. Daw, W. Windl, N. N. Carlson, M. Laudon, and M. P. Masquelier, "Effect of stress on dopant and defect diffusion in Si: A general treatment," *Phys. Rev. B, Condens. Matter*, vol. 64, pp. 045205-1–045205-10, Jun. 2001.

- [10] M. Laudon, N. N. Carlson, M. P. Masquelier, M. S. Daw, and W. Windl, "Multiscale modeling of stress-mediated diffusion in silicon: *Ab initio* to continuum," *Appl. Phys. Lett.*, vol. 78, pp. 201–203, Jan. 2001.

- [11] S. T. Dunham, M. Diebel, C. Ahn, and C. L. Shih, "Calculations of effect of anisotropic stress/strain on dopant diffusion in silicon under equilibrium and nonequilibrium conditions," *J. Vac. Sci. Technol. B, Microelectron. Process. Phenom.*, vol. 24, pp. 456–461, Jan./Feb. 2006.

- [12] M. J. Chen and Y. M. Sheu, "Effect of uniaxial strain on anisotropic diffusion in silicon," *Appl. Phys. Lett.*, vol. 89, pp. 161908-1–161908-3, Oct. 2006.

- [13] Y. M. Sheu, S. J. Yang, C. C. Wang, C. S. Chang, L. P. Huang, T. Y. Huang, M. J. Chen, and C. H. Diaz, "Modeling mechanical stress effect on dopant diffusion in scaled MOSFETs," *IEEE Trans. Electron Devices*, vol. 52, no. 1, pp. 30–38, Jan. 2005.

- [14] H. Tsuno, K. Anzai, M. Matsumura, S. Minami, A. Honjo, H. Koike, Y. Hiura, A. Takeo, W. Fu, Y. Fukuzaki, M. Kanno, H. Ansai, and N. Nagashima, "Advanced analysis and modeling of MOSFET characteristic fluctuation caused by layout variation," in VLSI Symp. Tech. Dig., 2007, pp. 204–205.

- [15] J. Welser, J. L. Hoyt, and J. F. Gibbons, "NMOS and PMOS transistors fabricated in strained silicon/relaxed silicon-germanium structures," in *IEDM Tech. Dig.*, 1992, pp. 1000–1002.

- [16] S. E. Thompson, M. Armstrong, C. Auth, M. Alavi, M. Buehler, R. Chau, S. Cea, T. Ghani, G. Glass, T. Hoffman, C. H. Jan, C. Kenyon, J. Klaus, K. Kuhn, Z. Ma, B. Mcintyre, K. Mistry, A. Murthy, B. Obradovic, R. Nagisetty, P. Nguyen, S. Sivakumar, R. Shaheed, L. Shifren, B. Tufts, S. Tyagi, M. Bohr, and Y. El-Mansy, "A 90-nm logic technology featuring strained-silicon," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1790–1797, Nov. 2004.

- [17] C. H. Ge, C. C. Lin, C. H. Ko, C. C. Huang, Y. C. Huang, B. W. Chan, B. C. Perng, C. C. Sheu, P. Y. Tsai, L. G. Yao, C. L. Wu, T. L. Lee, C. J. Chen, C. T. Wang, S. C. Lin, Y. C. Yeo, and C. Hu, "Process-strained Si (PSS) CMOS technology featuring 3D strain engineering," in *IEDM Tech. Dig.*, 2003, pp. 73–76.

- [18] A. Hamada, T. Furusawa, N. Saito, and E. Takeda, "A new aspect of mechanical stress effects in scaled MOS devices," *IEEE Trans. Electron Devices*, vol. 38, no. 4, pp. 895–900, Apr. 1991.

- [19] J. S. Lim, S. E. Thompson, and J. G. Fossum, "Comparison of threshold-voltage shifts for uniaxial and biaxial tensile-stressed n-MOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 11, pp. 731–733, Nov. 2004.

- [20] W. Zhao, A. Seabaugh, V. Adams, D. Jovanovic, and B. Winstead, "Opposing dependence of the electron and hole gate currents in SOI MOSFETs under uniaxial strain," *IEEE Electron Device Lett.*, vol. 26, no. 6, pp. 410–412, Jun. 2005.

- [21] X. Yang, J. Lim, G. Sun, K. Wu, T. Nishida, and S. E. Thompson, "Strain-induced changes in the gate tunneling currents in p-channel metaloxide-semiconductor field-effect transistors," Appl. Phys. Lett., vol. 88, pp. 052108-1–052108-3, Jan. 2006.

- [22] J. S. Lim, X. Yang, T. Nishida, and S. E. Thompson, "Measurement of conduction band deformation potential constants using gate direct tunneling current in n-type metal oxide semiconductor field effect transistors under mechanical stress," *Appl. Phys. Lett.*, vol. 89, pp. 073509-1–073509-3, Aug. 2006.

- [23] C. Y. Hsieh and M. J. Chen, "Measurement of channel stress using gate direct tunneling current in uniaxially stressed n-MOSFETs," *IEEE Electron Device Lett.*, vol. 28, no. 9, pp. 818–820, Sep. 2007.

- [24] C. Gallon, G. Reimbold, G. Ghibaudo, R. A. Bianchi, R. Gwoziecki, S. Orain, E. Robilliart, C. Raynaud, and H. Dansas, "Electrical analysis of mechanical stress induced by STI in short MOSFETs using externally

- applied stress," *IEEE Trans. Electron Devices*, vol. 51, no. 8, pp. 1254–1261, Aug. 2004.

- [25] R. A. Bianchi, G. Bouche, and O. Roux-dit-Buisson, "Accurate modeling of trench isolation induced mechanical stress effects on MOSFET electrical performance," in *IEDM Tech. Dig.*, 2002, pp. 117–120.

- [26] I. D. Wolf, "Micro-Raman spectroscopy to study local mechanical stress in silicon integrated circuits," *Semicond. Sci. Technol.*, vol. 11, pp. 139–154, 1906

- [27] C. Herring and E. Vogt, "Transport and deformation-potential theory for many-valley semiconductors with anisotropic scattering," *Phys. Rev.*, vol. 101, pp. 944–961, Feb. 1956.

- [28] I. Balslev, "Influence of uniaxial stress on the indirect absorption edge in silicon and germanium," *Phys. Rev.*, vol. 143, pp. 636–647, Mar. 1966.

- [29] C. G. Van de Walle and R. M. Martin, "Theoretical calculations of heterojunction discontinuities in the Si/Ge system," *Phys. Rev. B, Condens. Matter*, vol. 34, pp. 5621–5634, Oct. 1986.

- [30] H. H. Mueller and M. J. Schulz, "Simplified method to calculate the band bending and the subband energies in MOS capacitors," *IEEE Trans. Electron Devices*, vol. 44, no. 9, pp. 1539–1543, Sep. 1997.

- [31] L. F. Register, E. Rosenbaum, and K. Yang, "Analytic model for direct tunneling current in polycrystalline silicon-gate metal-oxide-semiconductor devices," *Appl. Phys. Lett.*, vol. 74, pp. 457–459, Jan. 1999.

- [32] S. Suthram, J. C. Ziegert, T. Nishida, and S. E. Thompson, "Piezoresistance coefficients of (1 0 0) silicon n-MOSFETs measured at low and high (~1.5 GPa) channel stress," *IEEE Electron Device Lett.*, vol. 28, no. 1, pp. 58–61, Jan. 2007.

- [33] K. N. Yang, H. T. Huang, M. J. Chen, Y. M. Lin, M. C. Yu, S. M. Jang, C. H. Yu, and M. S. Liang, "Edge hole direct tunneling in off-state ultrathin gate oxide p-channel MOSFETs," in *IEDM Tech. Dig.*, 2000, pp. 679–682.

- [34] K. N. Yang, H. T. Huang, M. J. Chen, Y. M. Lin, M. C. Yu, S. M. Jang, D. C. H. Yu, and M. S. Liang, "Characterization and modeling of edge direct tunneling (EDT) leakage in ultrathin gate oxide MOSFETs," *IEEE Trans. Electron Devices*, vol. 48, no. 6, pp. 1159–1164, Jun. 2001.

- [35] K. N. Yang, H. T. Huang, M. J. Chen, Y. M. Lin, M. C. Yu, S. M. Jang, D. C. H. Yu, and M. S. Liang, "Edge hole direct tunneling leakage in ultrathin gate oxide p-channel MOSFETs," *IEEE Trans. Electron Devices*, vol. 48, no. 12, pp. 2790–2795, Dec. 2001.

Chen-Yu Hsieh (S'06) received the B.S. degree in material science and engineering from the National Tsing-Hua University, Hsinchu, Taiwan, R.O.C., in 2002, and the M.S. degree in electronics engineering in 2004 from the National Chiao-Tung University, Hsinchu, where he is currently working toward the Ph.D. degree.

His current research interests include characterization and modeling of the strained-Si MOSFETs and the trap physics in nanoscale devices.

Ming-Jer Chen (S'78–M'79–SM'98) received the B.S. degree (with highest honors) in electrical engineering from the National Cheng-Kung University, Tainan, Taiwan, R.O.C., in 1977, and the Master's and Ph.D. degrees in electronics engineering from the National Chiao-Tung University (NCTU), Hsin-Chu, Taiwan, in 1979 and 1985, respectively.

In 1985, he joined the Department of Electronics Engineering, NCTU, where he is currently a Full Professor since 1993. From 1987 to 1992, he was a Consultant for the Taiwan Semiconductor Manufacturing

Company (TSMC), where he led a team from the NCTU and the Electronics Research and Service Organization (ERSO/ITRI) to build up a series of process windows and design rules. From 2000 to 2001, he was a Visiting Professor in the Department of Electrical Engineering, Stanford University, Stanford, CA. He is the holder of eight U.S. patents and six Taiwanese patents in the field of high-precision analog capacitors, 1-T memory cell, dynamic threshold MOS, electrostatic discharge protection, and Flash memory. His current research interests include semiconductor device physics and nanoelectronics.

Prof. Chen is a member of the Phi Tau Phi.