# 蕭特基能障金氧半電晶體元件研製與理論分析-總計畫

計畫編號: NSC 90-2215-E-009-079

執行期限: 90 年 08 月 01 日至 91 年 07 月 31 日

主持人:黃調元 國立交通大學電子研究所 共同主持人:林鴻志 國家奈米元件實驗室

## 一、摘要

在本研究計畫中,我們結合蕭特基能障電晶 體與新式場引發汲極延伸(field-induced drain)的結 構,可有效的壓抑在汲極端所產生的高電場,抑制 大漏電流的現象,使得元件的特性更加理想,得到 對於 n 通道和 p 通道而言, On/Off 電流的比率分 別為 10<sup>6</sup>和 10<sup>8</sup>。在計畫中,將並詳細研討蕭特基 能障薄膜電晶體的漏電流機制。具有場引發汲極延 伸的新式蕭特基能障薄膜電晶體擁有良好的雙極 性元件特性, 並能有效抑制類似閘極引發汲極漏電 流(GIDL)的 off-state 漏電流, 這種漏電流幾乎使 得傳統結構的特基能障薄膜電晶體不具操作特性. 對傳統結構元件而言,經由對其 off-state 的漏電 流的活化能(activation energy)之探究, 我們認 為由汲極端而來的載子場發射(field emission) 現象是主要的漏電流機制. 然而對具有 FID 結構的 原件而言,因為在汲極延伸區的費米能階被固釘在 靠近導電帶附近(對 nMOS 而言)所以熱離子發射 (thermionic)發射現象將取而代之,這導致對閘極 引發汲極漏電流的有效抑制.

#### **Abstract**

In this study, we have fabricated Schottky barrier (SB) MOSFET on SOI wafers. In this study, we have proposed and demonstrated new SB MOSFET devices that incorporated the field-induced-drain (FID) structure in an effort to reduce the large leakage current. We obtained the on/off current ratio for n- and p-channel devices to be  $10^6$  and  $10^8$ . Conduction mechanisms for the off-state leakage in Schottky barrier thin-film transistor were

explored. The new SBTFT device with FID extension shows excellent ambipolar performance with effective suppression of gate-induced drain leakage (GIDL)-like off-state leakage that conventional SBTFT devices. It was found that field-emission process dominates the leakage conduction of the device with conventional structure as the field strength in the drain junction becomes high, and results in the strong GIDL (gate-induced drain leakage)-like phenomenon. In contrast, for the device with field-induced-drain structure, the high-field region is pulled away from the silicide drain. As a result, thermionic emission rather than field emission becomes the dominant conduction mechanism, resulting in the effective suppression of the undesirable GIDL-like leakage current.

**Keywords**: SOI, Schottky barrier, field-induced drain (FID), field emission, thermionic emission.

#### 二、緣由和目的

蕭特基能障電晶體是目前深具潛力的元件,其元件的製作方式是由金屬源/汲極取代傳統離子植入的方式[1]-[5],它的好處包含:較簡單與低溫化製程,對短通道效應能有效抑制,免除離子佈植步驟與其回火動作,另有雙極性(ambipolar)元件特性[5],相當適用於未來奈米級元件的應用。蕭特基能障電晶體傳統上是由自我對準金屬矽化製程形成源/汲極[1]-[5],氧化矽邊襯可有效的避免源/汲極矽化物與閘極產

生橋接現象。然而,蕭特基能障電晶體具有嚴重的漏電流與較差的 On/Off 電流比率,同時在 off-state 時的漏電流表現類似 GIDL 的特性,特別是其值隨閘極與汲極間電壓的增加而增加[1]-[11],大大的抑制其實用性。

近幾年為了要彌補以上的缺失,我們 提出並成功的研製了一種具有場引發汲極 FID的SB MOSFETs[8]-[10]這種新結構, 這種新式結構的元件和傳統的蕭特基能障 電晶體結構類似,除了在通道與蕭特基汲 極間有一個 FID 存在。此外,它亦與具 FID 的金氧半電晶體類似[12][13],除了經由 離子摻雜而形成的汲極與源極以金屬矽化 物取代。更重要的是,在傳統結構中的類 似於 GIDL 的漏電流現象在新結構中可被 完全消除;然而,即使結果令人振奮,但 仍缺少對兩種結構之漏電流機制的瞭解, 在本計畫中,我們分別對兩種結構在不同 偏壓條件下施以便溫量測以對漏電流現象 進行分析. 基於所得的結果, 我們將討論漏 電流的傳導機制並證實之。

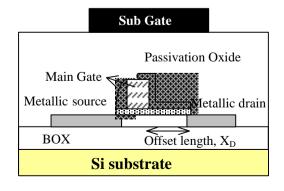

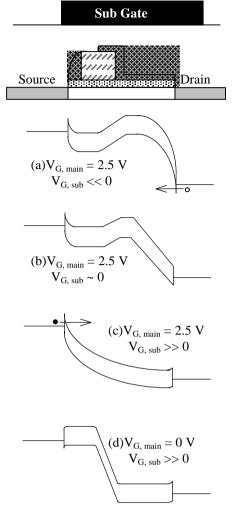

蕭特基能障電晶體的元件結構如圖 1 所示。在元件運作時,我們在副閘極上加 一個固定電壓以在 off-set 通道區形成一 個汲極延伸。因此,依照副閘極電壓的極 性,我們可以設定它以 n 型或 p 型操作,即 當副閘極電壓為負時,就是 p 型通道元 件,反之則是 n 型通道元件。

#### 三、結果與討論

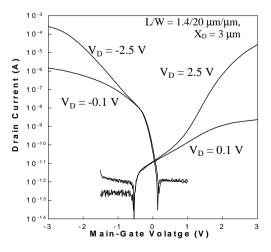

圖 2 為 SOI 蕭特基能障電晶體採用新式場引發汲極的電流特性圖,當操作於 N 通道或 P 通道,on/off 電流比率分別可達到  $10^7$ 或  $10^8$ ,此外,當採用此新式結構,關閉漏電流與閘極電壓大小並沒有相對關係。由圖中可觀察到,元件操作於 P 通道的特性遠優於操作於 N 通道,主要是因為

鎳金屬矽化的蕭特基能障對於電洞(約0.4 eV)遠低於電子(約0.7 eV)[14]。

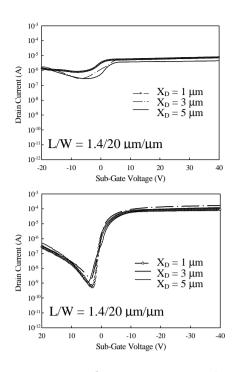

圖 3 顯示次閘極電壓,對於元件操作 於 N 通道( $V_{G,main} = +2.5$ )與 P 通道( $V_{G,main}$ =-2.5)的汲極電流影響,將此特性與圖2 比較可以明顯看出具有大漏電流,特別是 在N通道操作的模式下,而且會隨著次閘 極電壓的大小而改變。由圖4對四種不同 狀態的 N 通道能帶圖說明之前狀況,圖 4 中  $(V_{G,main} = +2.5 V, V_{G,sub} << 0)$  的大電 流,主要來自於汲極端的高電場電洞穿 透,不過此現象會隨著 VG.sub 逐漸增加至 0 V 而減小;當 V<sub>G,sub</sub>增加至一大正電壓時, 相當於元件正常導通的情形(V<sub>Gmain</sub> = +2.5 V, 圖 4C), 從源極端的高電場電子 穿透會成為主要的汲極電流來源[2]-[5], 换句話說,當 V<sub>G.main</sub> 切換至關閉狀態(如  $V_{G,main} \sim 0V$ ),且  $V_{G,sub}$ 維持在高正電壓, 在偏移區的電場感應汲極會抑制汲極漏電 流(即電洞的高電場穿透)[6],此關係如 圖 5D 所示,所以可有效的減小元件關閉 狀態的汲極漏電流。

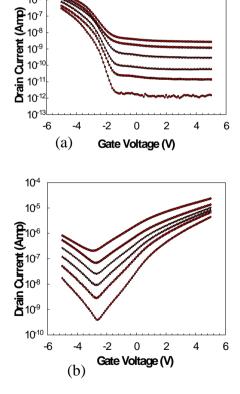

圖 5(a)是傳統蕭特基能障薄膜電晶體從攝氏25度到150度變溫量測之p型通道的次臨限 Id-Vg 特性圖。元件尺寸為W=20ìm, L=5ìm在這些圖裡面我們可以看到因為 off-state 漏電流太大的關係,導致整個元件絲毫沒有工作的可行性。事實上,我們還發現 off-state 漏電流對存在於主閘極和汲極間的電壓差非常敏感,因為整個 I-V 曲線是 V 字形的。

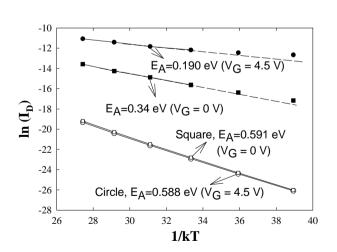

從變溫量測而得的 Arrhenius 圖中我們可以萃取出電流導通的活化能。在圖 6中我們展示了p型操作的活化能實例.在這些例子中, $|V_G|=0$  or 4.5 V, and  $|V_D|=1$  or 3 V.基本上我們可以看到,對某一固定的  $V_G$  來說, $E_A$  將隨著  $V_D$  的增加而下降;同時對一個固定的  $V_D$  而言, $E_A$  將

隨著  $V_D$  的增加而下降  $V_G$  的增加而下降。以上的趨勢在圖 6 中將更加明顯,在其中我們以  $E_A$  為  $V_G$  的函數而作圖,結果顯示, $E_A$  對  $V_{GD}$  來講非常敏感。從這個結果我們可得到如下的暗示,即在汲極區的電場強度對漏電流有很關鍵的影響。

圖 5(b)同樣也可用於解釋具有 FID 結構的蕭特基能障薄膜電晶體的變溫量測圖,操作於 p 型通道汲極延伸區  $X_D$  的長度為 4i m, W=20i m, L=5i m, 與傳統結構一樣。我們可以看到,儘管隨溫度上生會有漏電流增加的現象,但漏電流值和  $V_G$  之大小並沒有多大的關係.這個結果和傳統結構的結果形成明顯的對比。不過漏電流對溫度的相關性卻較大些,這暗示了導通機制似乎是個熱激發過程。

藉由蕭特基薄膜電晶體的變溫量測中,我們可以更加掌握蕭特基薄膜電晶體的漏電流機制,這有助於我們將來製作更短通道的 SOI 蕭特基電晶體。

## 四、參考文獻

- [1] M. P. Lepselter and S. M. Sze, *Proc. of IEEE*, pp.1400-1401, 1968

- [2] J. R. Tucker, C. Wang, and P. A. Carney, Appl. Phys. Lett., vol.65, pp.618-620, 1994.

- [3] W. Saitoh, A. Itoh, S. Yamagami, and M. Asada., *Jpn. J. Appl. Phys.*, vol.38, pp.6226-6231, 1999.

圖 1 SOI SB MOS device 的結構圖。.

- [4] J. Kedzierski, P. Xuan, J. Bokor, T. J. King, and C Hu, in *IEDM Tech. Dig.*, 2000, pp.57-60.

- [5] M. Nishisaka, Y. Ochiai, and T. Asano, in *Proc. Device Res. Conf. (DRC)*, 1998, pp.74-75.

- [6] C. Wang, J. P. Snyder and J. R. Tucker: Appl. Phys. Lett. 74 (1999). 1174

- [7] A. Itoh, M. Saitoh and M. Asada: Jpn. J. Appl. Phys. 39 (2000). 4757

- [8] H.C. Lin, C.Y. Lin, K.L. Yeh, T.Y. Huang, and S.M. Sze, in *IEDM Tech. Dig.*, 2000, pp.857-859.

- [9] H. C. Lin, K. L. Yeh, R. G. Huang, and T. Y. Huang, *IEEE Electron Device Lett.*, Vol.22, pp.179-181, 2001.

- [10] K. L. Yeh, H. C. Lin, R.G. Huang, R. W. Tsai and T. Y. Huang: Appl. Phys. Lett. 79 (2001).635

- [11] H. C. Lin, K. L. Yeh, R. G. Huang, and T. Y. Huang, in *AMLCD Tech. Dig.*, 2001, pp.247-250.

- [12] T. Y. Huang, I.W. Wu, A. G. Lewis, A. Chiang and R. H. Bruce: IEEE Electron Device Lett. **11** (1990). 244

- [13] T. Y. Huang, I.W. Wu, A. G. Lewis, A. Chiang and R. H. Bruce: IEEE Electron Device Lett. **11** (1990).541

- [14] S. M. Sze, *Physics of Semiconductor Devices*, 2<sup>nd</sup> Ed., 1982, p.292.

圖 2 元件電流-電壓圖。次閘極電壓分別為 30 和-30 V 對 n- 及 p-通道操作而言。

圖 3 次閘極電壓對於 n 或 p 通道元件的影響。 閘極和汲極電壓分別固定為 2.5V 或 -2.5V。

10-4

10<sup>-5</sup> 10<sup>-6</sup>

圖 5 蕭特基薄膜電晶體 p 通道的 Id-Vg 特性圖。 (a) 具 FID 結構。(b) 傳統結構。

圖 4 不同 n 通道操作電壓對於元件能階示意圖。

圖 6 蕭特基薄膜電晶體 p 通道的 Arrhenius plots。 (空白圓形為具 FID 結構,實心圓形為傳統 結構。)