# 行政院國家科學委員會補助專題研究計畫成果報告

※※※※※※※※※※※※※※※※※※※※※※※※※※※※

※ 超薄閘極氧化層元件可靠性研究 ※

※ Ultra-thin Gate Dielectric CMOS Device Reliability ※

※

※※※※※※※※※※※※※※※※※※※※※※※※※※※※

計畫類別： 個別型計畫 整合型計畫

計畫編號：NSC 90-2215-E-009-069-

執行期間：90 年 08 月 01 日至 91 年 07 月 31 日

計畫主持人：汪大暉 教授

計畫參與人員：博士生 蔡慶威、陳旻政、詹前泰

碩士生 江欣凱、李兆琪

執行單位：國立交通大學電子工程學系

中 華 民 國 91 年 10 月 25 日

# 超薄閘極氧化層元件可靠性研究

## Ultra-thin Gate Dielectric CMOS Device Reliability

計畫編號：NSC 90-2215-E-009-069

執行期限：90 年 8 月 1 日至 91 年 7 月 31 日

主持人：汪大暉 國立交通大學電子工程學系

### 一、中文摘要

本計畫著重於超薄閘氧化層元件所發生的可靠性問題。首先，吾人發現在超薄氧化層元件中由價帶電子穿隧所引發的熱載子退化機制，這種由歐傑復合所造成的元件退化現象和基極電壓成正相關，對於 SOI 和 DTMOS 元件將會造成嚴重的可靠性問題。另外在 SOI 元件中，由於氧化層軟崩潰後的電流增加，可能增強 SOI 中的浮接基底效應。由於軟崩潰位置的不同(通道軟崩潰及汲極軟崩潰)所造成的臨界電壓遲滯現象也將在本計畫中一一探討。

**關鍵詞：**超薄閘氧化層，歐傑復合，價帶電子穿隧，SOI，DTMOS，軟崩潰

### Abstract

This project addresses the issues related to ultra-thin gate oxide reliability. First, Auger recombination enhanced hot carrier degradation with stress  $V_g$  in the valence-band tunneling regime is observed. The enhanced degradation exhibits positive dependence on substrate bias and may cause a severe reliability issue in floating substrate devices (SOI) or positively biased substrate devices (DTMOS). In the second part, the floating body effect can be enhanced in SOI devices due to oxide soft breakdown. The location effect (channel or drain-edge) of soft breakdown on threshold voltage ( $V_t$ ) hysteresis will be explored and identified.

**Keywords:** ultra-thin gate oxide, Auger recombination, valence-band tunneling, SOI, DTMOS, soft breakdown.

### 二、計劃緣由與目的

隨著 CMOS 元件尺寸繼續縮小，氧化層厚度亦必須相對的降低以達到所預期的元件特性。當到達  $0.07\mu\text{m}$  製程時，預估所使用的氧化層厚度約為  $1.5\text{nm}$ ，在這樣薄氧化層中，由於 conduction band 電子發生 direct tunneling，閘極漏電流因此佔元件漏電流之主要部份。除此，亦可能產生一些新的可靠性議題與新的機制，其中 valence band 電子會發生 direct tunneling，而導致通道內電洞增加，並藉由一些復合機制(如 Auger recombination [1-3])而產生更高能量的熱電子，進而使元件特性退化。

另外，浮接基底效應[4-6]由於氧化層的軟崩潰位置的不同，可能在 SOI 元件中產生不同的影響。在通道軟崩潰中，由 valence-band tunneling 所產生多餘的電洞，將使得臨界電壓( $V_t$ )在閘極電壓交替時產生遲滯現象。另一方面，在汲極軟崩潰的元件中，當汲極電壓交替時，臨界電壓遲滯現象是由 band-to-band tunneling current)增加所導致的。

在本研究中吾人將探討由 valence band tunneling 所引發的熱載子可靠度問題，並在 SOI 元件中研究由軟崩潰位置不同所增強的遲滯效應。

### 三、結果與討論

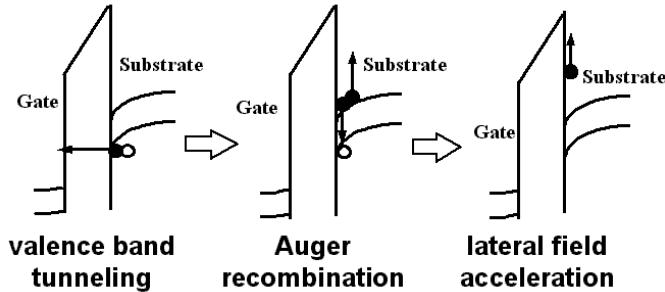

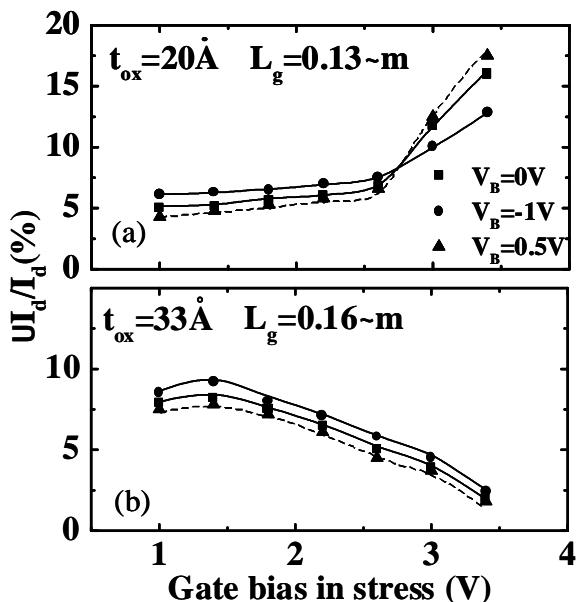

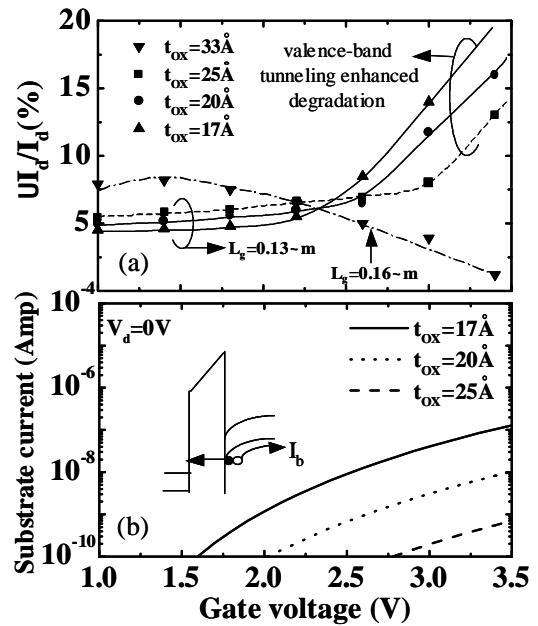

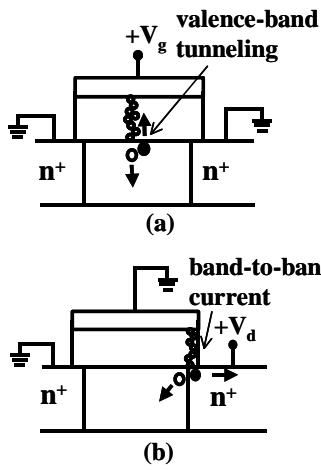

吾人發現一種在超薄氧化層中由 valence band tunneling 所產生新的熱載子退化現象[3]。此種退化機制如圖一所示，通道內因 valence band electron tunneling 產生電洞，再經由 Auger Process 產生高能量電子，最後，這些高能量電子會經由電場加速，獲得更高能量而產生破壞性。如圖二所示，此種元件熱載子破壞並不會隨著氧化層變薄而有改善的跡象，相反地在閘

極偏壓位於 valence band tunneling 區域時，在薄氧化層上的破壞反而是最嚴重的。相較之下，較厚的氧化層( $t_{ox}=33\text{ \AA}$ )由於沒有 valence band tunneling 發生，其熱載子退化情形和傳統觀念是一致的。

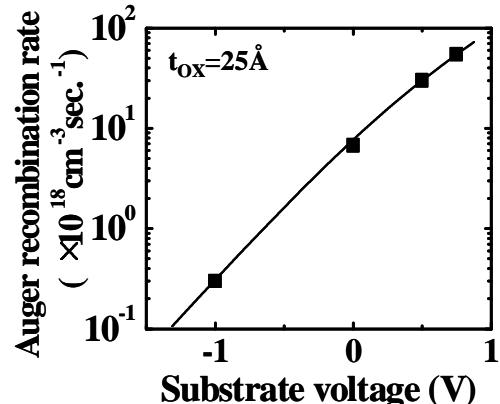

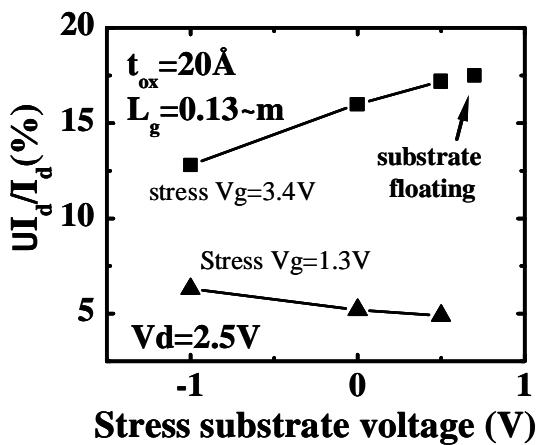

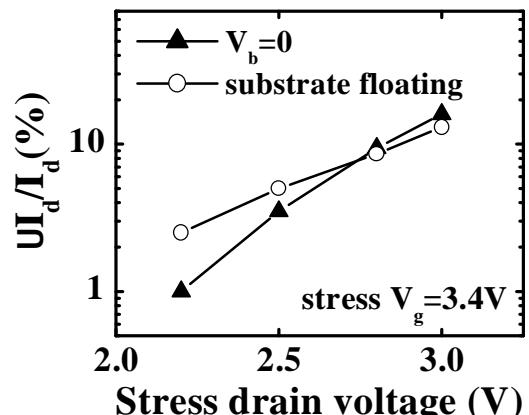

藉由基底偏壓的改變，吾人可以調變通道中的電洞濃度來觀察元件退化情形。如圖三所示，在閘極偏壓位於 valence band tunneling 時，其元件特性退化在正基底偏壓下較大，其原因可以由圖四解釋，當基底偏壓為負值時，通道中電洞的受到基底偏壓的吸引而傾向基底外排出，電洞濃度的降低可以有效地抑制通道中的歐傑復合效率。另外，在圖三較厚的氧化層及較低的閘極偏壓中，並不會有 valence band tunneling 發生，因此其基底偏壓效應並沒有上述之現象，而呈現一般的負基底偏壓相關性。在圖五中，這樣的正基底偏壓相關性造成了基底浮接的 SOI 元件(正基底偏壓)有較為顯著的元件特性退化。吾人並發現了此種退化機制在汲極偏壓降低時有更為顯著的趨勢(如圖六)，而成為在基底浮接的 SOI 元件，及在正基底偏壓操作下的 DTMOS 元件中，人們所關心的可靠度新議題。

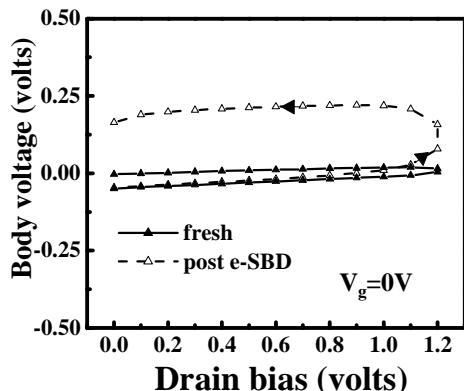

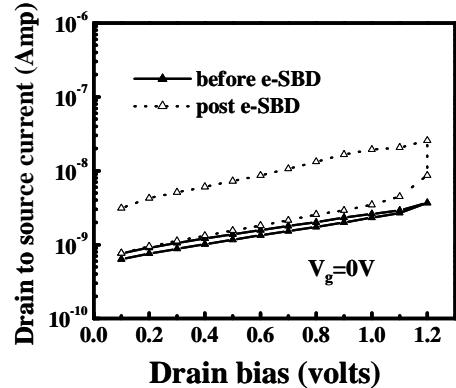

在 SOI 元件研究中，吾人發現了在氧化層軟崩潰之後，由於破壞位置不同所造成的浮接基底效應，這種效應是屬於元件關閉時的基底充電機制，和過去研究所著重的元件開啟狀態[4-5]明顯相異。吾人首先藉由量測方法[7]判斷軟崩潰之後的氧化層破壞位置，並將其分為通道軟崩潰及汲極軟崩潰兩種，如圖七所示，當發生通道軟崩潰時，由於可視為有效氧化層變薄，valence band tunneling 造成更多的電洞堆積在 SOI 基底而影響基底電位；另外一方面當氧化層發生汲極軟崩潰時，由於在汲極端的 band to band tunneling 增強，也造成了更多的電洞而影響基底電位。

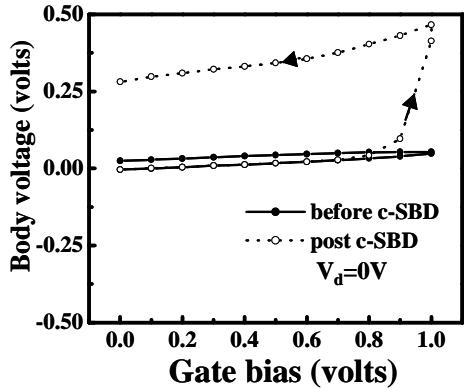

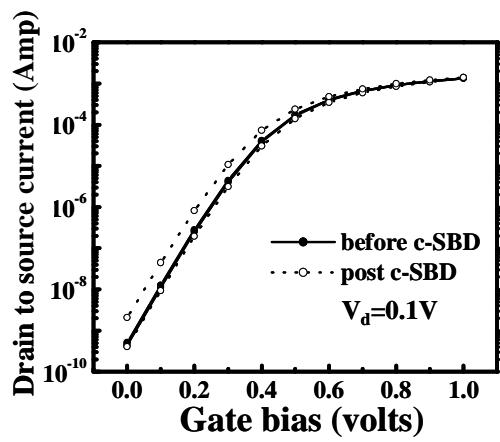

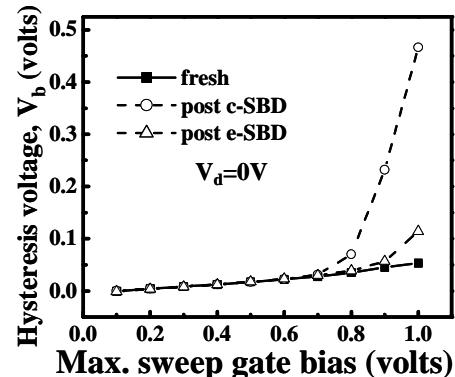

在圖八中，吾人發現在通道軟崩潰之後的操作電流隨著閘極電壓的交替會有一明顯的遲滯現象，此遲滯現象的來源可以由圖九解釋。在最大閘極電壓大於 1V 時(即 valence band tunneling 大幅增加)，其基底電位受到更多電洞的調變，而造成了基底

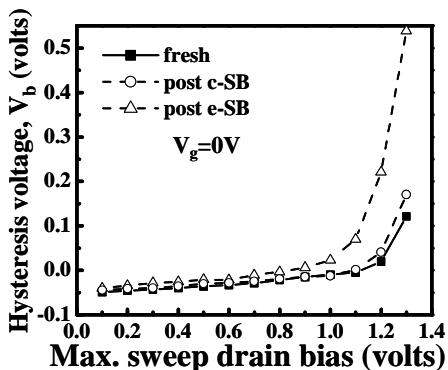

電位及臨界電壓的遲滯現象。另外，在圖十中，在汲極軟崩潰之後操作電流隨著汲極電壓的交替會有遲滯現象，藉由基底電位的量測(如圖十一)，吾人也可以發現基底電位呈現由 band to band tunneling 增強所造成的遲滯現象。

圖十一和圖十二針對遲滯現象的程度和操作電壓做完整的比較。當閘極電壓交替時，其基底偏壓只有在通道軟崩潰的元件中才會有嚴重的遲滯現象；反之，在汲極電壓交替時，在汲極軟崩潰的元件中才會有明顯的遲滯現象。即使是在低於 1.2V 的電壓交替中，這種由軟崩潰位置不同而引發的遲滯現象仍然可以觀測的到。

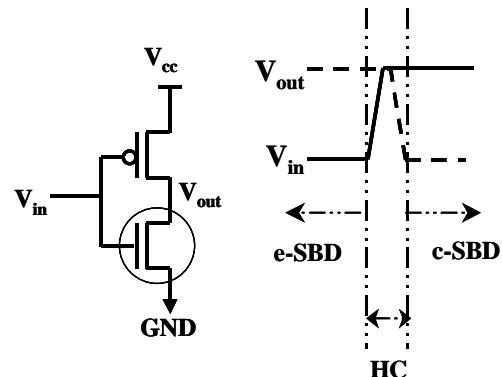

如圖十三所示，對於一組 CMOS 反向器來說，通道軟崩潰會對輸入為 1 的狀態造成影響，而汲極軟崩潰則是影響輸入為 0 的狀態，這兩種狀態雖然都是 CMOS 元件操作停止時的狀態，之後元件在開啟操作時的臨界電壓( $V_t$ )、轉移阻抗( $g_m$ )及通道電流( $I_d$ )都可能會被此軟崩潰所造成的浮接基底效應所影響。

#### 四、結論

本計畫對超薄氧化層元件中，由價帶電子穿隧所引發的熱載子退化機制做了一系列的探討，並預測在 SOI 和 DTMOS 元件中此超薄氧化層將會對元件造成嚴重的可靠性問題。在研究 SOI 元件方面，我們發現了由通道軟崩潰及汲極軟崩潰所分別造成的臨界電壓遲滯現象，此種基底浮接效應可能在低操作偏壓的 SOI CMOS 中造成電路穩定度的問題。

#### 五、參考文獻

- [1] M. Yamaji et al., *IEICE Trans. Electron.*, p.373 1994

- [2] L. P. Chiang et al., *VLSI Tech. Symp.*, p.132, 2000

- [3] C. W. Tsai et al., *IEDM Tech. Dig.*, p.139, 2000.

- [4] A. Boudou et al., *IEEE EDL*, vol. 8, p.300 1987.

- [5] S-K.H. Fung et al., *IEDM Tech. Dig.*, p.231, 2000.

- [6] M. C. Chen et al., *IRPS Proc.*, p.404, 2002.

- [7] R. Degraeve et al., *IRPS Proc.*, p.360, 2001.

圖一 價帶電子穿隧導致之熱電子形成過程。

圖三 不同基極加壓下的元件電流退化情形。

圖二 閘極電壓加壓下的元件電流退化情形

及其所對應的價帶電子穿隧電流。

圖四 在通道中所模擬的歐傑複合機率。

圖五 元件電流退化的正基極偏壓相關性及

負基極偏壓相關性。

圖六 元件電流退化的汲極偏壓相關性。

圖六 通道軟崩潰及汲極軟崩潰的介紹。

圖八 在通道軟崩潰之下的基極電位遲滯現象。

圖十 在汲極軟崩潰之下的基極電位遲滯現象。

圖十二 在汲極電壓交換之下的遲滯現象程度。

圖七 在通道軟崩潰之下的電流遲滯現象。

圖九 在汲極軟崩潰之下的電流遲滯現象。

圖十一 在閘極電壓交換之下的遲滯現象程度。

圖十三 在CMOS反向器中,不同位置軟崩潰所影響的操作區。