# 行政院國家科學委員會專題研究計畫 期末報告

高階助聽器晶片及系統--總計畫暨子計畫五：助聽器類比

積體電路設計(3/3)

計畫類別：整合型

計畫編號：NSC 101-2220-E-009-014-

執行期間：101年08月01日至102年10月31日

執行單位：國立交通大學電子工程學系及電子研究所

計畫主持人：吳介琮

共同主持人：楊順聰、桑梓賢、冀泰石、劉志尉、鄭裕庭

劉天仁

計畫參與人員：碩士級-專任助理人員：楊俊秀

碩士班研究生-兼任助理人員：許博豪

碩士班研究生-兼任助理人員：蔡元朗

碩士班研究生-兼任助理人員：藍家駿

碩士班研究生-兼任助理人員：吳書豪

博士班研究生-兼任助理人員：張智閔

博士班研究生-兼任助理人員：張家綾

報告附件：出席國際會議研究心得報告及發表論文

公開資訊：本計畫可公開查詢

中華民國 103 年 01 月 03 日

## 中文摘要：[總計畫]

本計畫將設計並實現一個能放置於耳道內（CIC/ITC, Completely-in-Canal/In-the-Canal）的高階數位式助聽器系統。除了助聽器的一般功能，如聽力補償、噪音抑制、回饋音消除等，本計畫將開發雙耳處理技術來進一步提升助聽器的效能。

在系統部分，本計畫將繼續改良針對華語而設計的聽力補償策略，並發展聽覺認知訊號處理技術以提升語音辨識力。同時我們將開發雙耳之間的通訊技術。左右耳助聽器可藉以互相溝通，交換訊號參數以平衡並且同步雙耳的助聽器，提供助聽器方向辨識的能力。更可進一步利用雙耳訊號聯合處理開發音源分離技術以提升噪音抑制的功能。本計畫將規劃臨床測試來評估所開發的助聽器的效益。

在硬體部分，本計畫將開發助聽器專用的 SoC 晶片，此晶片上有「助聽器計算引擎」，配合訊號處理加速器，可執行所有的助聽器訊號處理以及各種附加功能。我們將降低工作電壓來減少功率消耗。晶片上也會包含類比電路，用來將麥克風接收的訊號轉成數位訊號，以及將數位訊號轉成類比訊號並驅動喇叭。而晶片上的電源管理電路則是將電池電源轉換成穩定的電壓電源供其他電路使用。此 SoC 晶片將以 90 nm CMOS 製程技術製作，其整體功率消耗將小於 1 mW。本計畫也將開發高效能的微機電式喇叭、電感、及異質整合的微小型助聽器載具。所開發的載具可以整合聲學元件、晶片，及其他零件而成為完整之助聽器系統。

## [子計畫五]

本計畫是「高階助聽器晶片及系統」整合型計劃的一個子計畫。目的是設計及實現此系統所需要的低功率混合訊號式介面電路，並且將與其他數位電路整合於同一晶片上。本計劃將研發（1）類比數位轉換器；（2）數位 Class-D 喇叭驅動電路；（3）數位電源控制電路。本計畫是延續前一期計畫的研究成果，將發展新技術，改善以上電路的效能。

在麥克風接收端，訊號的頻寬有 20 kHz，而訊號的動態範圍（Dynamic Range）可高達 100 dB。我們已經研發出新型的 Delta-Sigma 類比數位轉換器（ADC），配合數位校正技術，可以簡化運算放大器而降低功率消耗。我們將改良此 ADC，增進其動態範圍並進一步降低功率消耗。我們會在前端加入可調整增益的放大器（Programmable-Gain Amplifier）來涵蓋麥克風的整個動態範圍。

在喇叭端的驅動電路將會是整個助聽器系統最耗電的部份。我們已經設計了一個高性能的 Class-D 喇叭驅動電路。我們將嘗試降低 Class-D 驅動電路的失真度。我們也會針對另一

個子計畫所開發的微機電喇叭，設計新的 Class-D 驅動電路。

本計畫的電源控制電路是從電池擷取能源，並提供穩定的電壓給系統中其他的電路使用。我們提出數位式的電源控制電路，藉以實現複雜的控制機制來提升電路的效能。此電源控制電路需要一個低功率的 ADC。我們會用 SAR (Successive-Approximation-Register) 的架構來實現此 ADC。

本計畫的所有電路最後將整合於 90 nm 的 CMOS 單晶片中。以 1 V 電池操作，類比電路的功率消耗不得超過 500 uW。

**中文關鍵詞：**助聽器、數位訊號處理器、低功率晶片系統、混合訊號式積體電路、微機電。

**英文摘要：** This project is to design and realize a completely-in-canal/in-the-canal (CIC/ITC) advanced digital hearing aid system. In addition to typical hearing aid functionalities, such as hearing-loss compensation, noise reduction, and echo cancellation, we will also develop binaural processing techniques to further improve the hearing aid performances. On the system design, we will continue improving the hearing-loss compensation strategy specifically designed for Chinese-speaking population. We will develop signal processing techniques rooted in understanding human hearing perception to achieve speech enhancement for hearing aid users. Furthermore, we will develop the communication technology for binaural hearing aids. Hearing aids on both the right ear and the left ear will be able to communicate and exchange signal parameters for the purpose of synchronizing and balancing them, thus preserving the directionality of the sound field. The joint processing of binaural signals can enable the acoustic source separation techniques which can be used to improve the efficiency of noise reduction. Actual clinical tryouts will be employed to evaluate the performance of the hearing aid functionalities we develop. On the hardware design, we will design several generations of hearing aid SoCs. The chips will include a digital computing engine and some hardware accelerators for executing all hearing-aid signal processing and other auxiliary functions. The

digital circuits are operated under reduced supply voltage to decrease power dissipation. Also on the chip are analog circuits, including analog-to-digital converters for converting microphone signals into digital signals, digital-to-analog converters for converting digital signals to speaker sounds. The power management circuits convert battery energy into stable supplies to power other circuits on the SoC. The chips will be fabricated using a 90 nm CMOS technology. Total power consumption of each SoC chip will be less than 1 mW. We will also develop high-efficient MEMS speakers, inductors, and heterogeneous micro carrier. This micro carrier can package acoustic devices, SoC chip, and other components to form a complete hearing aid system.

**英文關鍵詞：**Hearing Aids, Digital Signal Processor, Low-Power System on a Chip, Mixed-Signal Integrated Circuits, MEMS.

## 高階助聽器晶片及系統 (3/3) Advanced Hearing Aid SoC and System (3/3)

計畫編號 : NSC-101-2220-E-009-014

執行期限 : 自 101 年 8 月 1 日起至 102 年 7 月 31 日止

|       |               |             |

|-------|---------------|-------------|

| 主持人   | : 吳介琮         | 交通大學電子研究所   |

| 共同主持人 | : 楊順聰         | 馬偕醫學院全人教育中心 |

| 共同主持人 | : 冀泰石         | 交通大學電機研究所   |

| 共同主持人 | : 桑梓賢、周世傑、張添烜 | 交通大學電子研究所   |

| 共同主持人 | : 劉志尉、鄭裕庭     | 交通大學電子研究所   |

| 共同主持人 | : 劉天仁         | 馬偕醫院        |

Email : jt.wu@g2.nctu.edu.tw                    <http://www.alab.ee.nctu.edu.tw/wpjtwu/>

### 一、摘要

本計畫將設計並實現一個能放置於耳道內 ( CIC/ITC, Completely-in-Canal/In-the-Canal) 的高階數位式助聽器系統。除了助聽器的一般功能，如聽力補償、噪音抑制、回饋音消除等，本計畫將開發雙耳處理技術來進一步提升助聽器的效能。

在系統部分，本計畫將繼續改良針對華語而設計的聽力補償策略，並發展聽覺認知訊號處理技術以提升語音辨識力。同時我們將開發雙耳之間的通訊技術。左右耳助聽器可藉以互相溝通，交換訊號參數以平衡並且同步雙耳的助聽器，提供助聽器方向辨識的能力。更可進一步利用雙耳訊號聯合處理開發音源分離技術以提升噪音抑制的功能。本計畫將規劃臨床測試來評估所開發的助聽器的效益。

在硬體部分，本計畫將開發助聽器專用的 SoC 晶片，此晶片上有「助聽器計算引擎」，配合訊號處理加速器，可執行所有的助聽器訊號處理以及各種附加功能。我們將降低工作電壓來減少功率消耗。晶片上也會包含類比電路，用來將麥克風接收的訊號轉成數位訊號，以及將數位訊號轉成類比訊號並驅動喇叭。而晶片上的電源管理電路則是將電池電源轉換成穩定的電壓電源供其他電路使用。此 SoC 晶片將以 90 nm CMOS 製程技術製作，其整體功率消耗將小於 1 mW。本計畫也將開發高效能的微機電式喇叭、電感、及異質整合的微小型助聽器載具。所開發的載具可以整合聲學元件、晶片，及其他零件而成為完整之助聽器系統。

**關鍵詞:** 助聽器、數位訊號處理器、低功率晶片系統、混合訊號式積體電路、微機電。

## Abstract

This project is to design and realize a completely-in-canal/in-the-canal (CIC/ITC) advanced digital hearing aid system. In addition to typical hearing aid functionalities, such as hearing-loss compensation, noise reduction, and echo cancellation, we will also develop binaural processing techniques to further improve the hearing aid performances.

On the system design, we will continue improving the hearing-loss compensation strategy specifically designed for Chinese-speaking population. We will develop signal processing techniques rooted in understanding human hearing perception to achieve speech enhancement for hearing aid users. Furthermore, we will develop the communication technology for binaural hearing aids. Hearing aids on both the right ear and the left ear will be able to communicate and exchange signal parameters for the purpose of synchronizing and balancing them, thus preserving the directionality of the sound field. The joint processing of binaural signals can enable the acoustic source separation techniques which can be used to improve the efficiency of noise reduction. Actual clinical tryouts will be employed to evaluate the performance of the hearing aid functionalities we develop.

On the hardware design, we will design several generations of hearing aid SoCs. The chips will include a digital computing engine and some hardware accelerators for executing all hearing-aid signal processing and other auxiliary functions. The digital circuits are operated under reduced supply voltage to decrease power dissipation. Also on the chip are analog circuits, including analog-to-digital converters for converting microphone signals into digital signals, digital-to-analog converters for converting digital signals to speaker sounds. The power management circuits convert battery energy into stable supplies to power other circuits on the SoC. The chips will be fabricated using a 90 nm CMOS technology. Total power consumption of each SoC chip will be less than 1 mW. We will also develop high-efficient MEMS speakers, inductors, and heterogeneous micro carrier. This micro carrier can package acoustic devices, SoC chip, and other components to form a complete hearing aid system.

**Key Words:** Hearing Aids, Digital Signal Processor, Low-Power System on a Chip, Mixed-Signal Integrated Circuits, MEMS.

## 二、緣由與目的

人類的聽覺是一個很複雜的系統。如果一個人不容易聽清楚正常情況下的對話，表示他的聽力已經降低，會造成他溝通上的障礙，並影響他的生活品質。聽力降低的情形主要發生在老年人，原因是聽覺系統老化。在聽力降低的人當中，有一半是超過 65 歲的老年人。這類的聽力損失病例，大部分(85-90%)可以用助聽器改善。根據統計，人口中約有 10% 的人有聽力損失需要帶助聽器，也就是說全球約有 5 億人需要帶助聽器。但是在歐、美、日本、澳洲等先進國家聽障人口中助聽器之配帶率平約只有 16%。助聽器配帶之穿透率低有許多理由，其中包括：(1) 文化或社會對聽障不正常之偏見；(2) 助聽器的價格始終未降至一般大眾可接受的程度。單就 2000 年平均價是 US\$1183/Set；(3) 助聽器的功能未能說服一般大眾接受其效果/成本比。有關此點，大眾不滿之處分別是：一助聽器並沒有提供足夠的好處，甚至沒有幫助，尤其是指聽得到聲音但仍然聽不懂語音。二是助聽器在較為吵雜的環境下並沒有提供幫助，甚至放大噪音。三是配帶助聽器會造成耳朵不適。由這些原因來看目前的助聽器在設計上確實有許多需要改善的地方，例如助聽器要小、要輕、要簡單而且有效用。

一個非植入式的助聽器系統通常置於耳內或耳朵附近，其主要功能是將聲音訊號經由麥克風轉換成電訊號，再依據使用者的聽覺反應及習慣做適當的訊號處理，最後則藉由喇叭用音波刺激內耳的耳蝸。助聽器的訊號處理可以用類比式或數位式。類比式的訊號處理雖然有低功率消耗的優點，但是功能有限。因此現今的高階助聽器都是用數位式的訊號處理。助聽器是攜帶式系統，電池是主要能源，因此整體系統的功率消耗要極低，攜帶者才能長時間使用。助聽器的種類根據佩帶方式可分為 Behind the Ear (BTE)、In the Ear (ITE)、In the Canal (ITC)、Completely in the Canal (CIC) 等類。其中 BTE 型的助聽器體積最大，但也是目前功能最強大，銷售最普遍的類型。CIC 型的助聽器體積最小，可以完全隱藏於耳內，不容易被發覺。有效的助聽器功能需要用強大又省電的數位信號處理器 (Digital Signal Processor, DSP) 來實現。目前助聽器的訊號處理沒有一個公認有效的解決方案，助聽器廠商也不會詳細公布所使用的技術。助聽器用的 DSP 沒有統一的標準或規格，雖然市場上有公開銷售的助聽器 DSP，如 AMI Semiconductor 與 GENNUM 等公司的產品，多家助聽器廠商還是自行開發晶片。助聽器晶片除了 DSP 之外，還包括類比電路，用來接收微型麥克風的訊號並轉換成數位訊號，以及將 DSP 的輸出轉換成類比訊號並推動微型喇叭。在麥克風部分，目前微型 MEMS 麥克風的技術已經成熟。目前助聽器所使用的微型喇叭往往與 D 類 (Class-D) 功率放大器做成一體。樓氏電子 (Knowles Electronics) 是麥克風及其他助聽器周邊元件最主要的供應商。

本計畫團隊已經執行了一個 NSOC 助聽器計畫。經過三年的研究，我們已經發展出自己的聽力補償策略、回授效應抑制、以及雜訊消除等技術，並且將這些訊號處理移植到晶片上。在此新的一期計畫中，我們將持續研發新技術，來進一步提升助聽器的效能。我們也會持續開發新一代的助聽器晶片，加強功能，降低功率消耗。

在系統部分，本計畫將繼續改良針對華語而設計的聽力補償策略，並發展聽覺認知訊號處理技術以提升語音辨識力。同時我們將開發雙耳之間的通訊技術，讓左右耳的助聽器可以互相溝通。此技術可以用來平衡並且同步雙耳的助聽器，

提供助聽器方向辨識的能力。此技術還可以用來發展音源分離訊號處理技術以提升噪音抑制的功能。本計畫將規劃臨床測試來評估助聽器的效益。

在硬體部分，本計畫將開發助聽器專用的 SoC 晶片，此晶片上有「助聽器計算引擎」，配合訊號處理加速器，可執行所有的助聽器訊號處理以及各種附加功能。我們將降低工作電壓來減少功率消耗。晶片上也會包含類比電路，用來將麥克風接收的訊號轉成數位訊號，以及將數位訊號轉成類比訊號並驅動喇叭。而晶片上的電源管理電路則是將電池電源轉換成穩定的電壓電源供其他電路使用。此 SoC 晶片將以 90 nm CMOS 製程技術製作，其整體功率消耗將小於 1 mW。本計畫也將開發高效能的微機電式喇叭、電感、及異質整合的微小型助聽器載具。所開發的載具可以整合聲學元件、晶片，及其他零件而成為完整之助聽器系統。

### 三、研究方法及成果

本助聽器團隊組成於 2006/08，並且在 2007/08 至 2010/07 間執行 NSOC 國家型計畫之「助聽器晶片及系統」計畫。本計畫將延續先前的計畫，開發高階助聽器功能，設計新一代的 SoC 晶片，並且整合助聽器於一微小載具上。

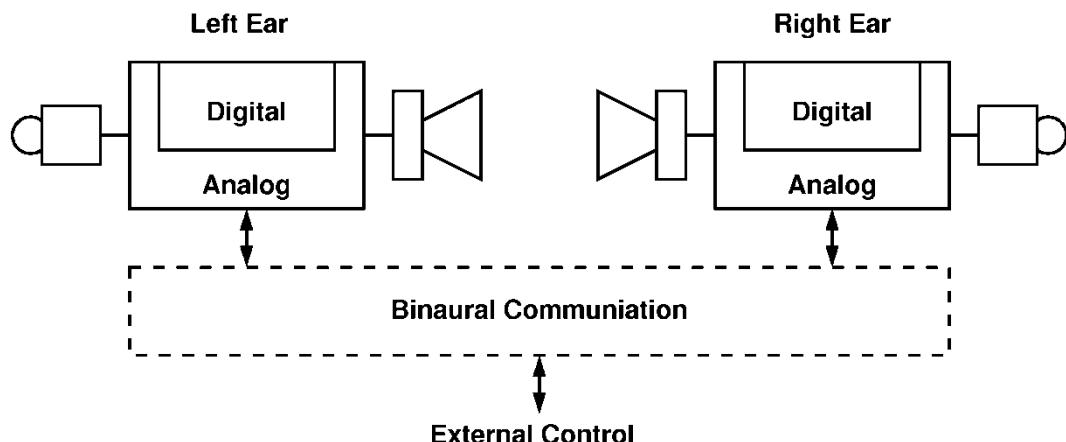

本計畫將設計並實現一個能放置於耳道內（CIC/ITC, Completely-in-Canal/In-the-Canal）的雙耳助聽器系統。如圖 3.0-1 所示，使用者的左耳與右耳各放一枚助聽器。個別的助聽器可以接收聲音訊號，經由微機電麥克風和電路轉換成數位訊號，用數位電路做聽力補償，最後藉由微機電喇叭產生音波刺激內耳的耳蝸。本計畫同時將規劃一個以頭顱做為通訊通道的低功率雙耳通訊系統。此通訊系統可以讓左右耳的助聽器互相交換資訊，提供方向辨識的能力，並且能更有效地抑制噪音，提升聲音品質。此外，使用者也可以藉由此通訊系統來控制助聽器，如調整音量大小、平衡雙耳音量、改變聽力補償參數等。

圖 3.0-1 雙耳助聽器系統示意圖。

本計畫必須結合不同領域的專長，包括助聽器系統、通訊系統、訊號處理、IC 設計、微機電等。分項子計畫分別為：

- 一、雙耳助聽器系統功能設計與效益評估

- 二、雙耳通訊技術

- 三、聽覺認知訊號處理

- 四、助聽器數位積體電路設計

- 五、助聽器類比積體電路設計

- 六、助聽器異質整合技術

其中「子計畫一」、「子計畫二」、「子計畫三」執行助聽器的系統設計。「子計畫一」將規劃雙耳助聽器系統，包括聽力補償策略、音源方向辨識、噪音抑制等功能。所開發的功能會以臨床測試來評估其效益。「子計畫二」將開發雙耳通訊技術，使得雙耳助聽功能得以實現。「子計畫三」將以更先進的聽覺模型來進行音源分離以抑制噪音，並針對聽障人士耳蝸之頻率解析能力建立模型，進而發展更有效益的聽力補償策略。

「子計畫四」、「子計畫五」、「子計畫六」將實現助聽器系統所需的硬體。所

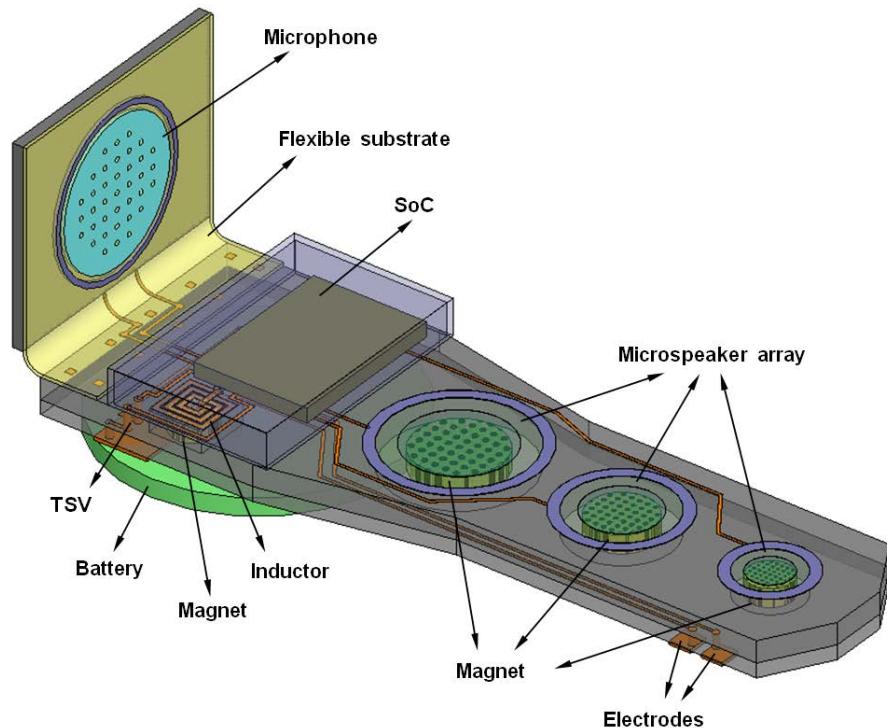

有的電路會整合於單一 SoC 晶片上。再用 SIP 技術整合晶片、聲學元件、及其他被動元件於一小型載具上，如圖 3.0-2 所示。「子計畫四」將設計數位電路，包括助聽器計算引擎、輔助訊號處理加速器、記憶體等電路。「子計畫五」將設計類比電路，包括類比數位轉換器、Class-D 放大器、以及電源管理電路等。所有的電路，將整合於 90 nm CMOS 的單晶片中。以 1 V 電池操作，預期的整體消耗功率要小於 1 mW。「子計畫六」將開發異質整合的微小型助聽器載具、微機電喇叭、以及微型電感。

另外，「子計畫四」將執行本計畫助聽器的臨床人體試驗。

圖 3.0-2 助聽器構造。

以下就各子計畫的研究方法以及成果逐一說明。

### 3.1 雙耳助聽器功能設計與驗證（楊順聰教授，馬偕醫學院全人教育中心）

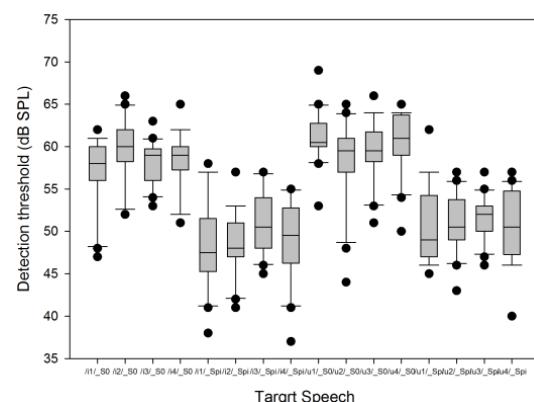

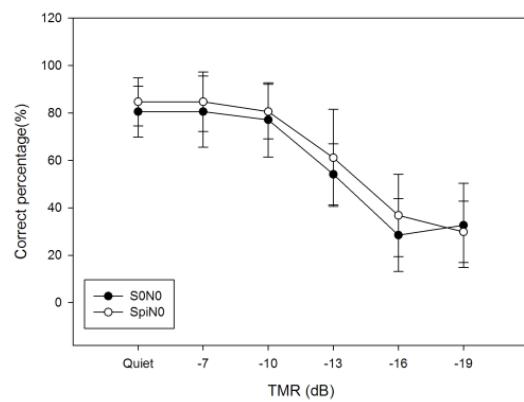

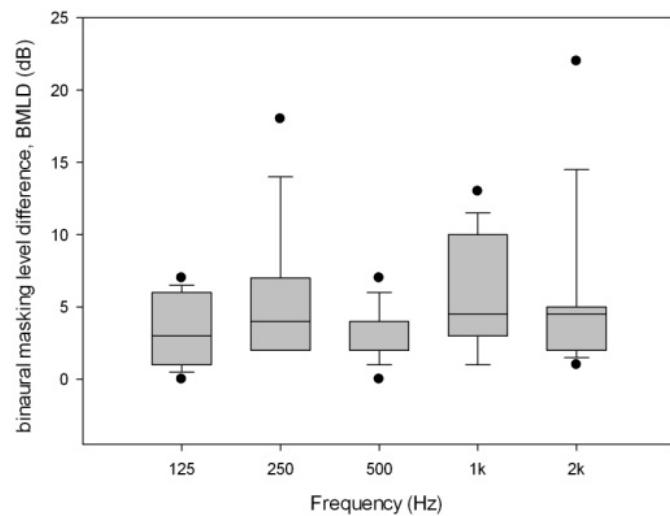

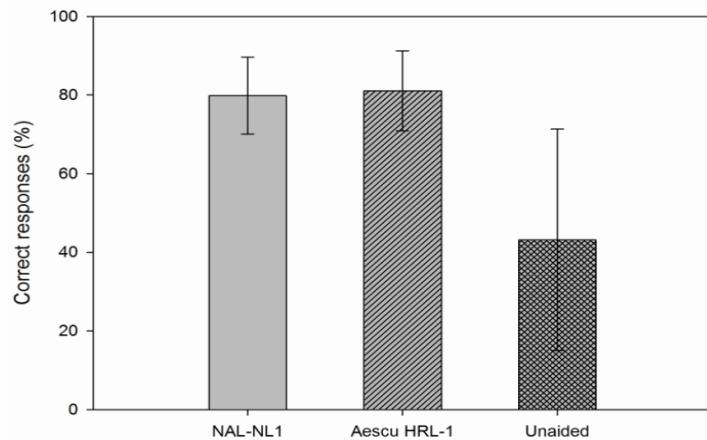

本子計畫之研究分為三部份，第一部份為雙耳功能聽知覺功能測試與驗證，主要藉由在遮蔽音下，藉由雙耳目標音相位的改變，觀察雙耳遮蔽位階效應(binaural masking level difference, BMLD)對於華語語音聲調察覺閾值(tone detection threshold, TDT)、華語聲調辨識百分比(tone discrimination score, TDS)之影響以及探討聽力損失者經助聽器補償後之雙耳遮蔽位階差異。第二部份為雙耳選配華語助聽器之臨床效益驗證。第三部份為適應性助聽器補償放大架構。以此三部份作為雙耳聽覺輔具訊號處理於提升華語語音理解度之前驅性研究。

#### 實驗結果

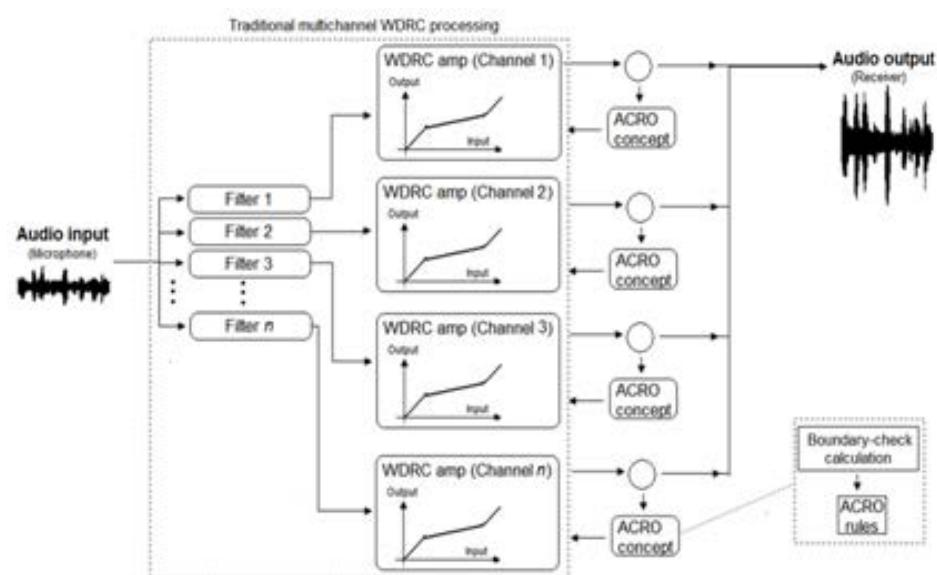

第一部份研究完成相關測試語音之設計、錄音以及電腦化測試平台、聽覺補償測試音箱設計，以及雙耳遮蔽位階差異於華語語音聲調察覺閾值、華語聲調辨識百分比之實驗。第二部份實驗結果 Aescu HRL-1 能有效的幫助聽力損失者提高語音理解度，並在主客觀之效果略佳於目前臨床上最為常用的 NAL-NL1 處方。第三部份實驗證實適應性助聽器補償放大架構能提供較佳之 SNR 值及足夠的補償增益給予受測者聆聽。

圖 3.1-1.a

圖 3.1-1.b

圖 3.1-1.a, 1.b 華語語音聲調察覺與聲調辨識百分比閾值於雙耳遮蔽位階異

圖 3.1-2 感音神經性聽損者經助聽器補償後之雙耳遮蔽位階差異

圖 3.1-3 客觀性華語單音節字音語音聽辨測驗

圖 3.1-4 適應性助聽器補償放大架構

### 3.2 助聽器雙耳通訊技術（桑梓賢教授，交通大學）

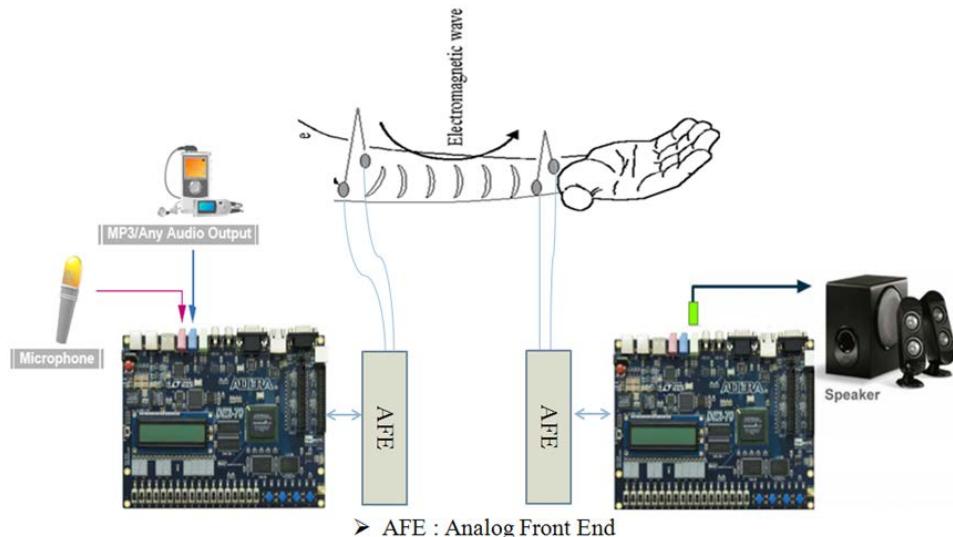

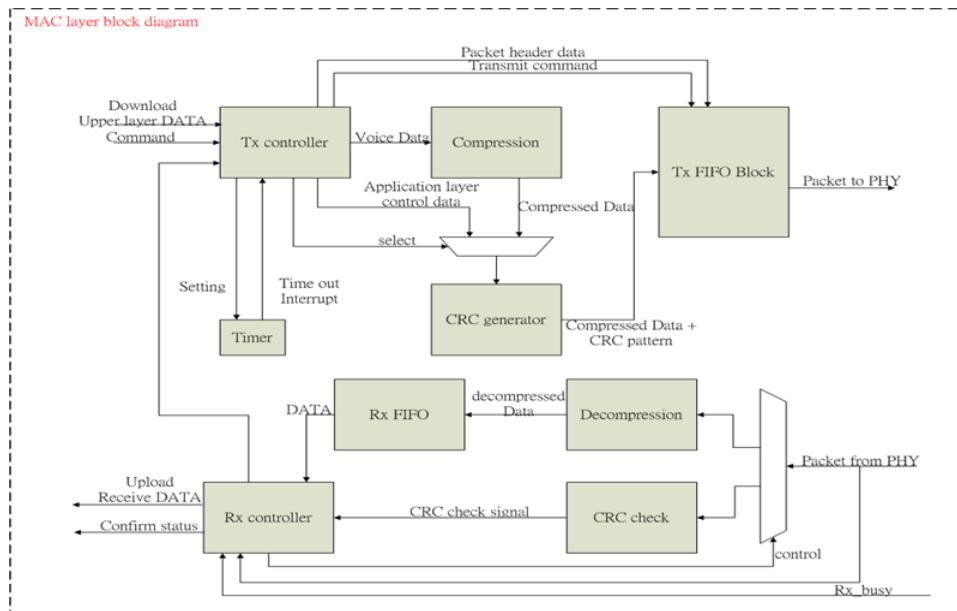

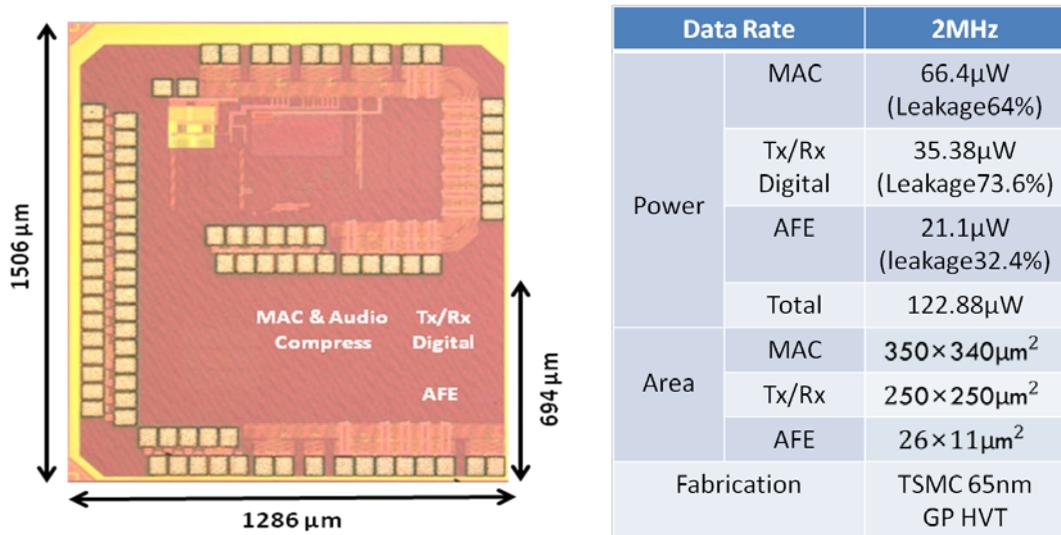

本子計畫為雙耳助聽器提供兩耳訊號互通一個穩定的通訊平台。在三年研究時光中，我們首先測定人體皮膚作為傳輸介質的通道狀況、釐清文獻中諸多混亂不合理的數據、建立自己的有效資料。我們和其他子計畫合作分析雙耳助聽器音頻訊號處理的需求、擬定通訊支援規格，據此開發適合低功耗雙耳通訊的通訊協定、資料格式及壓縮、調變方式、設計晶片、並實作通訊系統離形。成果計有：(一)、完成傳輸峰值達 2 Mbps 之低功耗雙耳通訊系統電路設計，完成晶片下線及測試。(二)、完成 FPGA/discrete component 系統離形實作，驗證皮膚傳導通訊技術支援雙耳助聽器可行性。(三)、完成音頻資料壓縮演算法和電路設計，可加入本通訊系統以增加傳輸效能。(四)、設計下一代皮膚傳導近身通訊系統，突破目前受限於低功耗低時間延遲以致傳輸效率較低的現狀。

圖 3.2-1 全穿戴式皮膚傳導通道量測實驗設置。

圖 3.2-2 皮膚傳導通訊系統離形。

圖 3.2-3 MAC Layer Block Diagram。

圖 3.2-4 通訊晶片及其規格。

### 3.3. 聽覺認知訊號處理（冀泰石教授，交通大學）

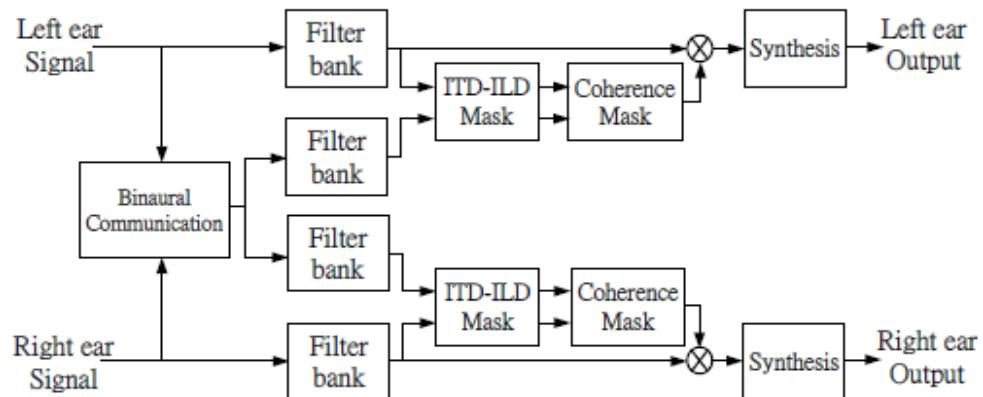

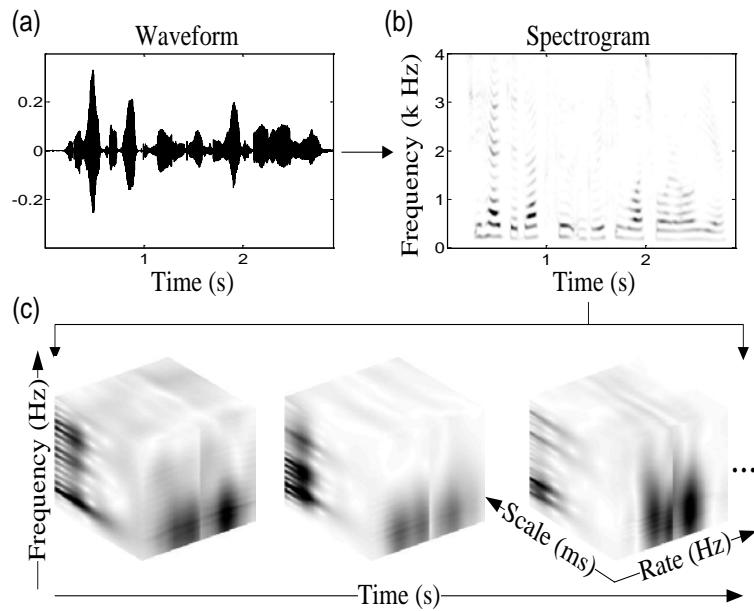

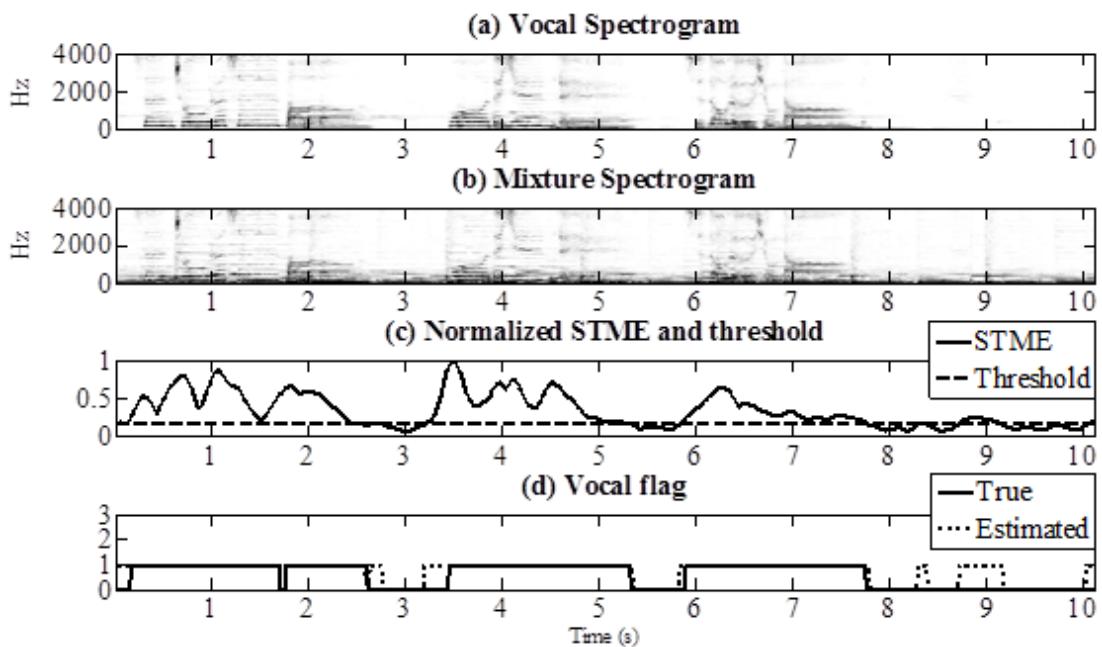

本計畫針對單雙耳抗噪議題完成下列幾項目標。第一，提出基於空間特徵的雙耳消噪演算法。此演算法中利用雙耳所收訊號之時間差(ITD)，能量差(ILD)，和一致性(coherence)等空間線索在時間-頻率(T-F)上進行遮蔽處理以達到分別壓抑方向性干擾源和散射雜訊(diffusion noise)的目的。第二，提出基於諧波頻率調變的語音端點偵測技術。此技術比三種標準的VAD: ITU-T G.729B、ETSI AMR1和AMR2在非平穩雜訊下的接收器操作特性(ROC)曲線和辨識率都有更好的表現，辨識率是在真實分佈式語音辨識(DSR)系統下進行測試。第三是發展基於頻域調變敏感度的感知迴音消除器。在過去，主要考量了人類在不同頻率下之聽覺閾值的感知聲學迴音消除器已被提出。在這研究裡，我們增加第二個預強調濾波器將大腦對於頻域調變的敏感度納入考量，以擴展感知正規化最小均方差演算法(P-NLMS)。模擬結果和聽力測試展示我們提出的演算法在收斂過程中能更有效地降低殘餘迴音。第四是建立基於時頻域調變之歌聲偵測結合音高群聚之歌聲分離技術。在此研究中，我們發展了一套基於時頻分析的歌聲偵測技術結合維特比音高搜尋演算法來實現單聲道歌聲分離，最終以估計出來的二元模板將具有諧波成分的歌聲從背景音樂伴奏中分離出來，實驗結果證明我們的技術比其它三種基於估計二元模板的技術要來的好。

圖 3.3-1 空間資訊的助聽器雙耳消噪演算法。

圖 3.3-2 基於諧波頻域調變的語音端點偵測。

圖 3.3-3 於時頻域調變之歌聲偵測結合音高群聚之歌聲分離技術。

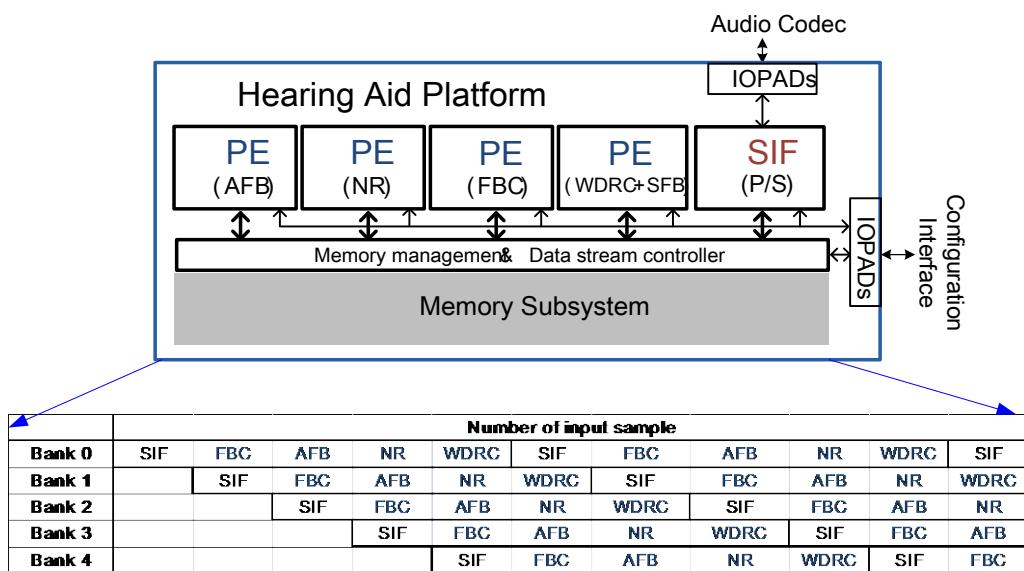

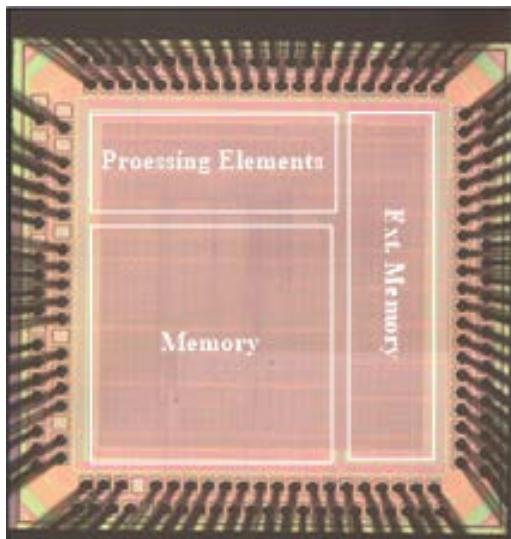

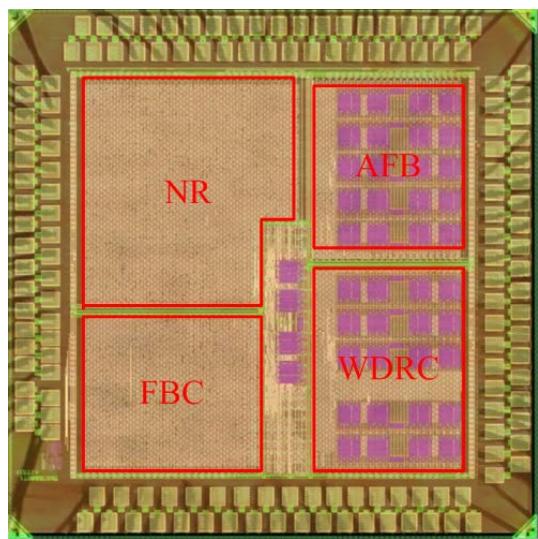

### 3.4. 助聽器數位積體電路設計（劉志尉教授，交通大學）

隨著積體電路以及訊號處理技術的快速發展，現代數位助聽器能夠大幅改善聽損者的生活品質。然而由於助聽器體積持續地縮小以及不斷地採用更多先進的訊號處理演算法來提升語音品質，其電池使用時間仍未必能讓使用者完全滿意，因此先進助聽器亟需低功耗的設計以及相對應的硬體實現來延長電池使用時間。本計畫針對助聽器的聽力補償運算、語音增強等方向，從演算法、硬體架構、以及電路實現上來探討其低功耗的設計。本計畫首先提出一個 18 頻帶的低複雜度 ANSI S1.11 1/3-octave 濾波器組，利用多率(multirate)的濾波器組架構設計來節省運算複雜度，並放寬低頻的規格，使其符合 10 ms 的延遲時間限制。本計畫亦提出適用於該濾波器組的聽損補償方式，使補償誤差控制於 1.5 dB 的範圍之內。考慮濾波器組的計算較為複雜，本計畫也提供一種不需分頻，僅靠單一濾波器的聽損補償方式。此外，本計畫亦發表適用於 Quasi ANSI S1.11 濾波器的仿神經音高式噪音消除設計，透過語音偵測模組及降噪模組，改善雜訊消除的效果。除上述演算法外，本計畫的低功耗濾波器計算方式改善了濾波器的效率。上述所有演算法均整合於一異質多核心的數位訊號處理器中，透過下線驗證其功能正確。該處理器經過本計畫所提的一種可變延遲設計方式，可工作於 0.5V 的低電壓以節省功率消耗。最後，本計畫與子計畫三共同開發雙耳助聽器的演算法，並提出頻率位移的濾波器設計方式，降低雙耳演算法的計算複雜度。

圖 3.4-1 異質多核心數位訊號處理器架構圖及資料交換流程。

圖 3.4-2 質多核心數位訊號處理器晶片。

圖 3.4-3 低電壓的異質多核心助聽器整合晶片。

圖 3.4-4 超低電壓的異質多核心助聽器離形。

### 3.5. 助聽器類比積體電路設計（吳介琮教授，交通大學）

本子計畫研發(1)類比數位轉換器；(2)數位 Class-D 喇叭驅動電路；(3)數位電源控制電路。在 1 V 的電源電壓之下，規劃的功率消耗分配如下；麥克風前置放大器與類比數位轉換器佔 150  $\mu$ W，微機電喇叭驅動電路佔 300  $\mu$ W，電源控制電路佔 50  $\mu$ W。

在麥克風接收端，我們用市面可購買到的原件設計並實現了一個麥克風可變增益放大器。此電路可以直接用於總計畫的助聽器 Prototype 系統中。而此經驗可幫助我們設計助聽器晶片中的麥克風放大器電路。

我們設計了一個音頻差積調變器 (Delta-Sigma Modulator, DSM)。此 DSM 已經用 TSMC 90 nm CMOS 製程製作成晶片，且量測成功。此 DSM 有 24.4 kHz 的訊號頻寬， $\pm 800$  mV 的差動輸入範圍，100 dB 的動態範圍。在 1 V 的電壓下操作，只消耗 860  $\mu$ W 的功率。

我們持續在設計一個我們設計了一個數位式 Class-D 喇叭驅動電路。為了降低功率消耗，我們採用 Pulse-Width Modulation (PWM) 的調變方式。數位音頻訊號會先經過一個內插器 (Interpolator) 進行超取樣。接著內插過後的訊號經過 Digital PWM 轉換成代表脈衝寬度的訊號。在轉成實際脈衝訊號之前，數位脈衝寬度訊號會透過一個 Noise Shaper 轉為較少位元訊號，如此便能在不損失訊號精確度的前提下降低 Pulse Generator 的時脈頻率，降低電路的功率消耗。最後，我們採用混合計數器與延遲線的架構來實現 Pulse Generator。此架構可以降低計數器的操作頻率並減少延遲單元數目以簡化延遲線的設計。我們提出了一個延遲線時間歪斜 (Timing Skew) 校正技術，可以補償因延遲線延遲單元間的時間歪斜所造成的 SNR 下降的問題。此數位式 Class-D 喇叭驅動電路已經完成設計與佈局，目前正在製作成晶片中。

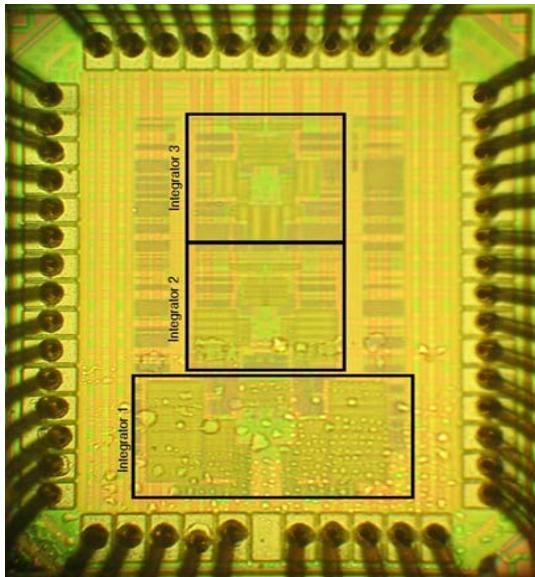

圖 3.5-1 差積調變器 (Delta-Sigma Modulator, DSM) 電路。

圖 3.5-2 DSM 晶片照片。

|                    |                              |

|--------------------|------------------------------|

| Technology         | 90 nm CMOS                   |

| Signal Bandwidth   | 24.4 kHz                     |

| Sampling Rate      | 6.25 MHz                     |

| Oversampling Ratio | 128                          |

| Input Range        | 500 mVpp                     |

| Peak SNDR (dB)     | 88                           |

| Dynamic Range      | 100 dB                       |

| SFDR (dB)          | 99                           |

| Supply Voltage     | 1.0 V                        |

| Power Dissipation  | 860 $\mu$ W                  |

| Active Area        | 560x780 $\mu$ m <sup>2</sup> |

表 3.5-1 DMS 晶片量測結果。

圖 3.5-3 數位 PWM 調變器。

圖 3.5-4 Class-D 放大器輸出級電路。

### 3.6. 助聽器異質整合技術（鄭裕庭教授，交通大學）

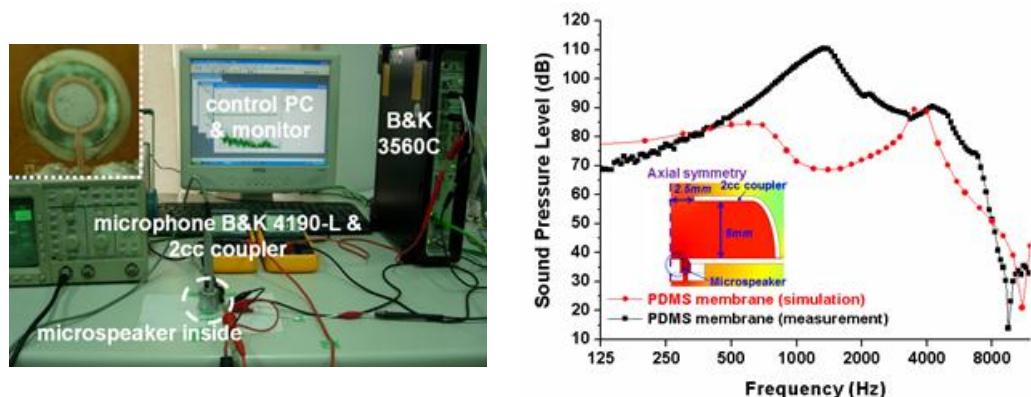

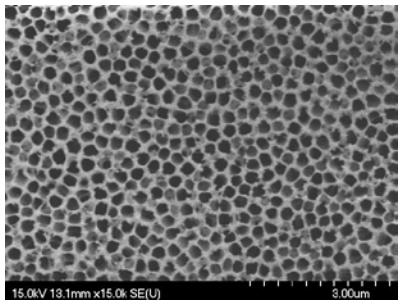

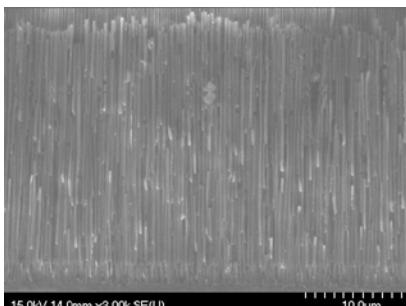

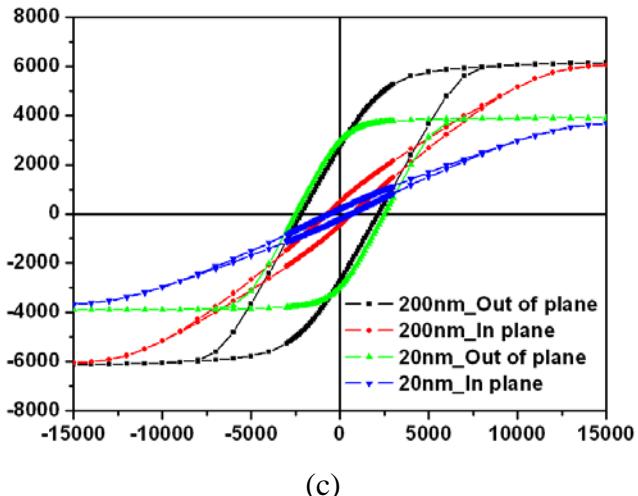

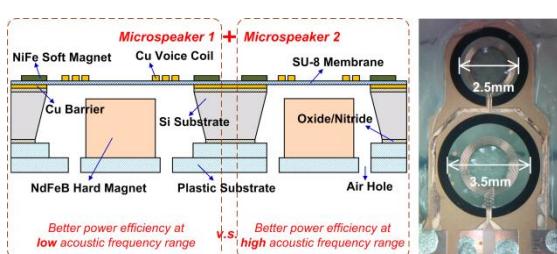

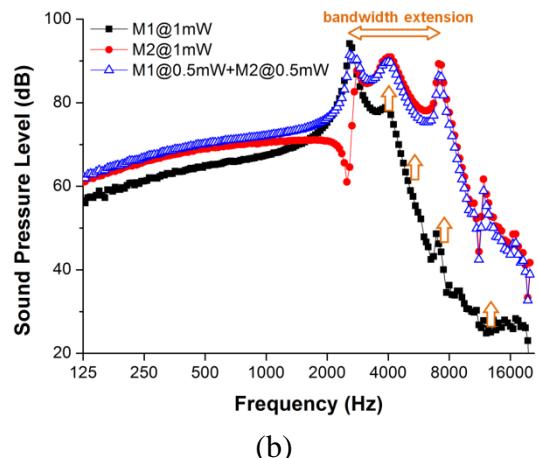

本計劃於三年執行期間共開發出四項應用於耳道型助聽器之技術，分別為(1)低溫軟性開發異質晶片整合所需之軟性連結線技術；(2)低功率電磁式微機電微型喇叭；(3)應用於電磁式微型揚聲器之永磁材料；以及(4)全域音源微型喇叭陣列。所開發出之軟性連結線可應用於生物醫學裝置，在一條具極低剛性之螺旋結構設計不僅可以增加連結線之平面位移，亦可有效緩解連結線對和元件之間之應力，增加元件使用之便利性與可靠度。低功率微瓦級電磁式揚聲器係使用 PDMS 作為電磁式微型揚聲器振膜，以電鍍銅層作為背部空腔濕蝕刻矽阻擋層來完成此振膜，此揚聲器振膜直徑為 3.5mm，厚度為  $3.3\mu\text{m}$ ，並且實驗結果顯示在 2cc 模擬耳道空間內，產生頻率為 1kHz, 106dB 聲壓級所需之功耗僅為 1.76mW。此外，以奈米孔洞陽極氧化鋁板製備具高深寬比結構特性( $>150$ )之鈷鎳錳燐奈米複合柱陣列永久磁鐵膜，具有矯頑磁:2512Oe，殘留磁場:3616Gauss，最大磁能積:12.02kJ/m<sup>3</sup> 等優異特性。相關永磁特性由於其製造與現今 CMOS Foundry 後段製程相容，此技術之應用除電磁式微型揚聲器外，亦可導入磁力計與微型發電機之製作。計畫最後一年，我們提出改善喇叭頻寬之方法，在單一個基板上製備對不同頻率最佳化之喇叭陣列，延展聲音輸出頻寬之低功率設計。整體輸出頻寬可由原先之 1kHz 提昇至 2.5kHz。總括本子計畫所開發之助聽器異質整合技術，將可推進未來超低功耗耳道型助聽器之發展。

圖 3.6-1:利用微加工技術所製作出之單晶矽微型探針(a)穿刺並置於豬心上之微型探針(b)與軟性電氣連結導線連接之矽微型探針。

圖 3.6-2:微型喇叭(a)量測設置與(b)輸出聲壓及其頻率響應結果。

(a)

(b)

(c)

圖 3.6-3:CoNiMnP-氧化鋁磁性納米複合膜 SEM 照片(a) 200nm 孔徑氧化鋁膜頂視圖和(b)沉積的 CoNiMnP-氧化鋁磁性納米複合膜截面視圖。

(a)

(b)

圖 3.6-4: 微揚聲器陣列，旨在延長工作頻率帶寬來優化功耗:(a)截面示意圖與製造出之陣列的照片，(b) 微揚聲器陣列量測結果:工作頻率帶寬來優化功耗的聲壓頻率響應。

## 四、結論

助聽器的歷史可追溯至西元 16 世紀時期，它也是當初發明電晶體的主要動機。然而從偏低的穿透率可知目前的助聽器在性能上仍然很大的改善空間。奈米積體電路技術的進步，使得助聽器從 90 年代開始數位化。本計畫希望能研發出新一代的數位式助聽器系統。

本團隊於 2006/08 開啟助聽器計畫。2006/08 至 2007/07 間執行「助聽器微機電晶片系統」國科會計畫。從 2007/08 起至 2010/07，我們執行「助聽器微機電晶片系統」國家型 NSOC 計畫。從 2010/08 起至 2013/07，我們執行「高階助聽器晶片及系統」國家型 NPIE 計畫。我們在交通大學建立的一個助聽器實驗室。此實驗室內有無響箱與無響室，可以做完整的聲學元件量測，以及助聽器的效能測試。

我們已經掌握了高階數位助聽器的主要關鍵性技術，如聽力補償策略、噪音抑制、回饋音消除、雙耳通訊、雙耳訊號處理低功率 IC 設計、MEMS 微型喇叭等。我們可以用 FPGA 展現一個助聽器原型系統。我們設計並製作 IC 晶片來實現我們開發的助聽器技術。

由於計畫經費不足以負擔晶片製作費用，因而無法確保製作晶片之製程與時程。Hard IP 如 Low-Voltage SRAM、類比電路等是使用不同製程設計。

由於新竹馬偕醫院無法找到合適且志願的聽障者，本計畫原先規畫的人體實驗因而延宕，導致目前無法完整的驗證本計畫所開發的硬體及新式聽力補償策略。然而本計畫另外有開發其他不需要人體實驗的技術，如噪音消除。此技術已經技轉予廠商。我們已經將部分的人體實驗轉與花蓮慈濟醫院李家鳳醫師合作。

由於本團隊資源有限，助聽器原形系統整合工作無法順利進行。我們有試圖尋找產業界的合作，希望以產學計畫方式，共同開發，整合晶片及系統。台灣本地的助聽器製造商的規模都不大，沒有財力投資 IC 設計。而由於助聽器晶片的市場目前很小，台灣的 IC 設計公司都不願意投入。本團隊曾接觸多家廠商，如明展生醫、元勛國際、美樂迪、瑞昱半導體、鑫創等，商討技術轉移的可能性。但是都沒有形成實際合作計畫。

本計畫開發的衍生性技術，如雜音消除，有技轉給 IC 設計公司。

本助聽器計畫涵蓋多項不同領域之專長，技術成果包括人類聽覺模型、針對華語之助聽補償策略、語音訊號處理技術、雙耳通訊技術、助聽器系統發展平台、超低功率微處理器與數位訊號處理器、超低功率系統晶片設計技術、超低功率類比電路設計技術、微機電式聲學元件、微機電異質整合封裝技術等。以上這些技術除了發展醫療用的助聽器之外，還可以應用於特殊聽覺感應系統、多媒體之高性能耳機、以及各種超低功率之晶片系統等。

# 助聽器類比積體電路設計(3/3)

## Analog interface Circuits for Hearing Aid SoC (3/3)

計畫編號 : NSC-101-2220-E-009-014

執行期限 : 自 101 年 8 月 1 日起至 102 年 7 月 31 日止

主持人 : 吳介琮 交通大學電子研究所

博士生 : 張智閔、張家綾、藍家駿、許博豪 交通大學電子研究所

Email : [jt.wu@g2.nctu.edu.tw](mailto:jt.wu@g2.nctu.edu.tw) http://www.alab.ee.nctu.edu.tw/wpjtwu/

### 一、摘要

本計畫是「高階助聽器晶片及系統」整合型計劃的一個子計畫。目的是設計及實現此系統所需要的低功率混合訊號式介面電路，並且將與其他數位電路整合於同一晶片上。本計劃將研發(1)類比數位轉換器；(2)數位 Class-D 喇叭驅動電路；(3)數位電源控制電路。本計畫是延續前一期計畫的研究成果，將發展新技術，改善以上電路的效能。

在麥克風接收端，訊號的頻寬有 20 kHz，而訊號的動態範圍(Dynamic Range)可高達 100 dB。我們已經研發出新型的 Delta-Sigma 類比數位轉換器(ADC)，配合數位校正技術，可以簡化運算放大器而降低功率消耗。我們將改良此 ADC，增進其動態範圍並進一步降低功率消耗。我們會在前端加入可調整增益的放大器(Programmable-Gain Amplifier)來涵蓋麥克風的整個動態範圍。

在喇叭端的驅動電路將會是整個助聽器系統最耗電的部份。我們已經設計了一個高性能的 Class-D 喇叭驅動電路。我們將嘗試降低 Class-D 驅動電路的失真度。我們也會針對另一個子計畫所開發的微機電喇叭，設計新的 Class-D 驅動電路。

本計畫的電源控制電路是從電池擷取能源，並提供穩定的電壓給系統中其他的電路使用。我們提出數位式的電源控制電路，藉以實現複雜的控制機制來提升電路的效能。此電源控制電路需要一個低功率的 ADC。我們會用 SAR( Successive-Approximation-Register ) 的架構來實現此 ADC。

本計畫的所有電路最後將整合於 90 nm 的 CMOS 單晶片中。以 1 V 電池操作，類比電路的功率消耗不得超過 500 uW。

關鍵詞：低功率類比電路、混合訊號式積體電路、助聽器。

This project is one of the sub-projects of the “Advanced Hearing Aid SoC and System” project. The objective is to design and realize the essential low-power mixed-signal interface circuits, and then integrate those circuits with other digital circuits on the same chip. This project will develop (1) an audio analog-to-digital converter; (2) a digital class-D speaker driver; and (3) a digital power management circuit. This project is a continuation of a previous research. We will develop new

techniques to improve circuit performances.

At the microphone end, the required signal bandwidth is 20 kHz and the dynamic range is as high as 100 dB. We have developed a new delta-sigma analog-to-digital converter (ADC) with digital calibration, which was used to reduce the power consumption of the operational amplifiers. We will improve the dynamic range of the existing design while further reducing its power consumption. We will also add a programmable-gain amplifier at the ADC input to cover the entire dynamic range of the microphone.

In a hearing aid system, the speaker drivers consume a significant portion of power. We have designed a high-efficient class-D speaker driver. We will further reduce the distortion of the driver. We will also design driver circuits for the MEMS micro speakers developed in a separate sub-project.

The power management circuit for this project is to extract energy from a battery and provide stable power supplies for other circuits. We have proposed a new digital power management technique to realize complex control mechanism while improving efficiency. The system requires a low-power ADC, which will be realized using the successive-approximation-register (SAR) architecture.

All circuits will be integrated on a single chip fabricated in a 90 nm CMOS technology. Operating under a 1 V battery supply, the total power consumption for the analog circuits will be less than 500 uW.

**Key Words:** Low-Power Analog Circuits, Mixed-Signal Integrated Circuits, Hearing Aids.

## 二、緣由與目的

本計畫所屬的總計畫「高階助聽器晶片及系統」是要設計並實現一個能放置於耳道內（CIC/ITC, Completely-in-Canal/In-the-Canal）的雙耳助聽器系統。在硬體部分，所有的電路會整合於單一 SoC 晶片上。數位電路包括助聽器計算引擎、輔助訊號處理加速器、記憶體等。類比電路包括類比數位轉換器、Class-D 放大器、以及電源管理電路等。所有的電路，將整合於 90 nm CMOS 的單晶片中。以 1 V 電池操作，預期的整體消耗功率要小於 1 mW。總計畫同時規劃了開發異質整合技術，可以將晶片、聲學元件、及其他被動元件整合於一小型載具上。

本子計畫將研發(1)類比數位轉換器；(2)數位 Class-D 喇叭驅動電路；(3)數位電源控制電路。本計畫是延續前一期計畫的研究成果，將發展新技術，改善以上電路的效能。

本計畫的所有電路最後將整合於 90 nm 的 CMOS 單晶片中。以 1 V 電池操作，類比電路的功率消耗不得超過 500 uW。

### 三、研究方法及成果

總計畫團隊於 2006/08 開啟助聽器計畫，並且在 2007/08 至 2010/07 間執行 NSOC 國家型計畫之「助聽器晶片及系統」計畫。本研究群於 2006/08 至 2010/07 間執行國科會之「助聽器類比介面電路」子計畫。本計畫是先前計畫的延續。

本子計畫將研發(1)類比數位轉換器；(2)數位 Class-D 喇叭驅動電路；(3)數位電源控制電路。在 1 V 的電源電壓之下，規劃的功率消耗分配如下；麥克風前置放大器與類比數位轉換器佔 150 uW，微機電喇叭驅動電路佔 300 uW，電源控制電路佔 50 uW。

在麥克風接收端，訊號的頻寬有 20 kHz，而訊號的動態範圍(Dynamic Range)可高達 100 dB。我們已經研發出新型的 Delta-Sigma 類比數位轉換器(ADC)，配合數位校正技術，可以簡化運算放大器而降低功率消耗。我們將改良此 ADC，增進其動態範圍並進一步降低功率消耗。我們會在前端加入可調整增益的放大器(Programmable-Gain Amplifier)來涵蓋麥克風的整個動態範圍。

在喇叭端的驅動電路將會是整個助聽器系統最耗電的部份。我們已經設計了一個高性能的 Class-D 喇叭驅動電路。我們將嘗試降低 Class-D 驅動電路的失真度。我們也會針對另一個子計畫所開發的微機電喇叭，設計新的 Class-D 驅動電路。

本計畫的電源控制電路是從電池擷取能源，並提供穩定的電壓給系統中其他的電路使用。我們提出數位式的電源控制電路，藉以實現複雜的控制機制來提升電路的效能。此電源控制電路需要一個低功率的 ADC。我們會用 SAR( Successive-Approximation-Register ) 的架構來實現此 ADC。

以下將針對本計畫目前的成果逐一介紹。

### 3A. 麥克風放大電路

數位助聽器最重要的考量是在嘈雜的環境下，類比前端放大電路(Analog Front-End)因為環境聲音加上背景雜訊造成飽和，而引發劇烈的效能劣化。背景雜訊干擾正常的聲音轉換，削弱了可理解的音訊。使用高動態範圍(Dynamic Range)的類比前端放大電路可以紓解此問題，但是付出了功率消耗及電路複雜度的代價。

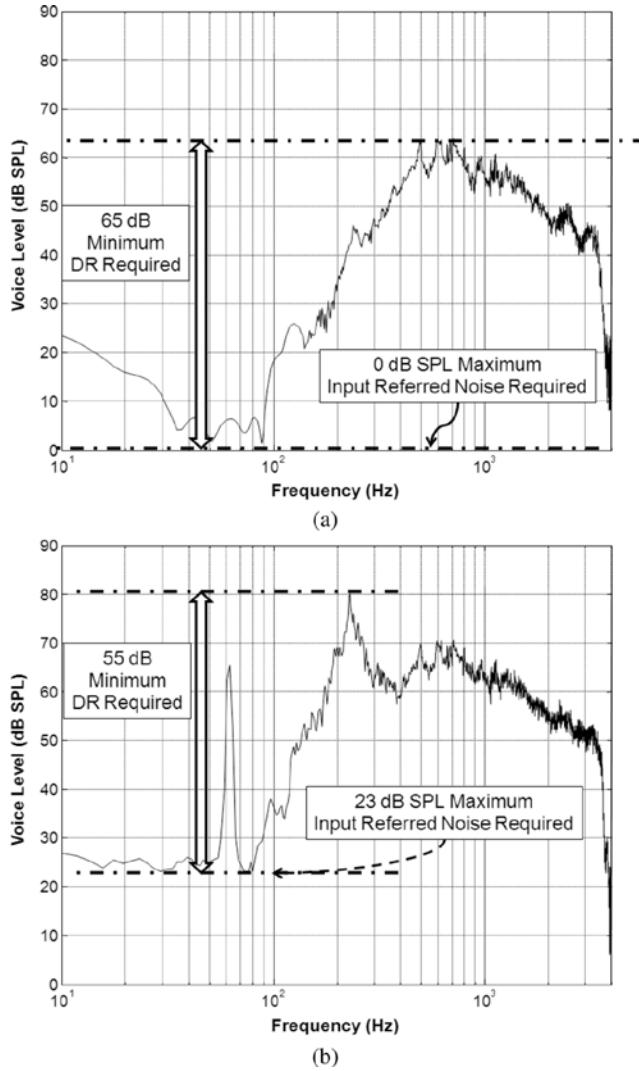

一般來說，音頻訊號處理電路的動態範圍及功率大小會隨著不同的環境具有不同的特徵。如 Fig.3A.1 所示[Deligoz 10]，Fig.3A.1(a)是在一個安靜的環境的轉換量測到的頻譜，其雜訊層大約為 0dB SPL(Sound Pressure Level)，音頻訊號動態範圍約是 65dB。Fig.3A.1(b)是一個嘈雜的環境下的轉換(如街道上)，其雜訊層升高至 25dB SPL，而此時的動態範圍僅剩下 55dB。傳統上的助聽器架構具有一個固定的動態範圍(例如 120dB)來對抗不同的背景雜訊，但如此一來功率消耗增加。本計劃中使用適應性控制機制(Adaptive Control Mechanism)，在不同的背景雜訊中調整系統的線性度(Linearity)以及訊號雜訊比(SNR)，盡可能的延長電池的使用時間。

Fig.3A.1. 量測雜訊層(noise floor)的功率頻譜密度(PSD)(a)在安靜的環境下; (b)在吵雜的環境下

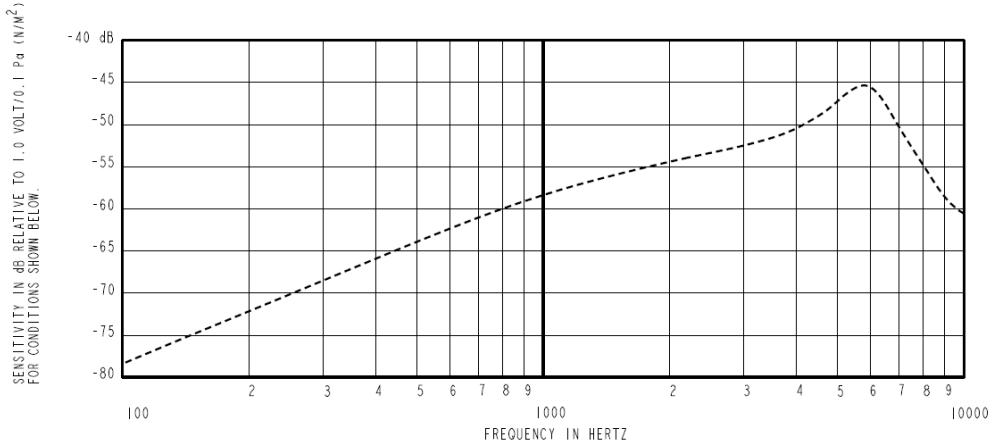

本計劃實行上述方法採用一個低雜訊可變增益放大器(Low-Noise Variable-Gain amplifier)。此電路為實作晶片的樣板 Fig.3A.3，未來在晶片完成後，將與後端電路整合成系統。本電路是基於一樓氏(Knowles EM-24047)電容式微機電麥克風(Capacitive MEMS Microphone)為輸入而設計，此麥克風的靈敏度頻率響應圖如 Fig.3A.2 所示。

Fig.3A.2. 微機電麥克風靈敏度頻率響應圖

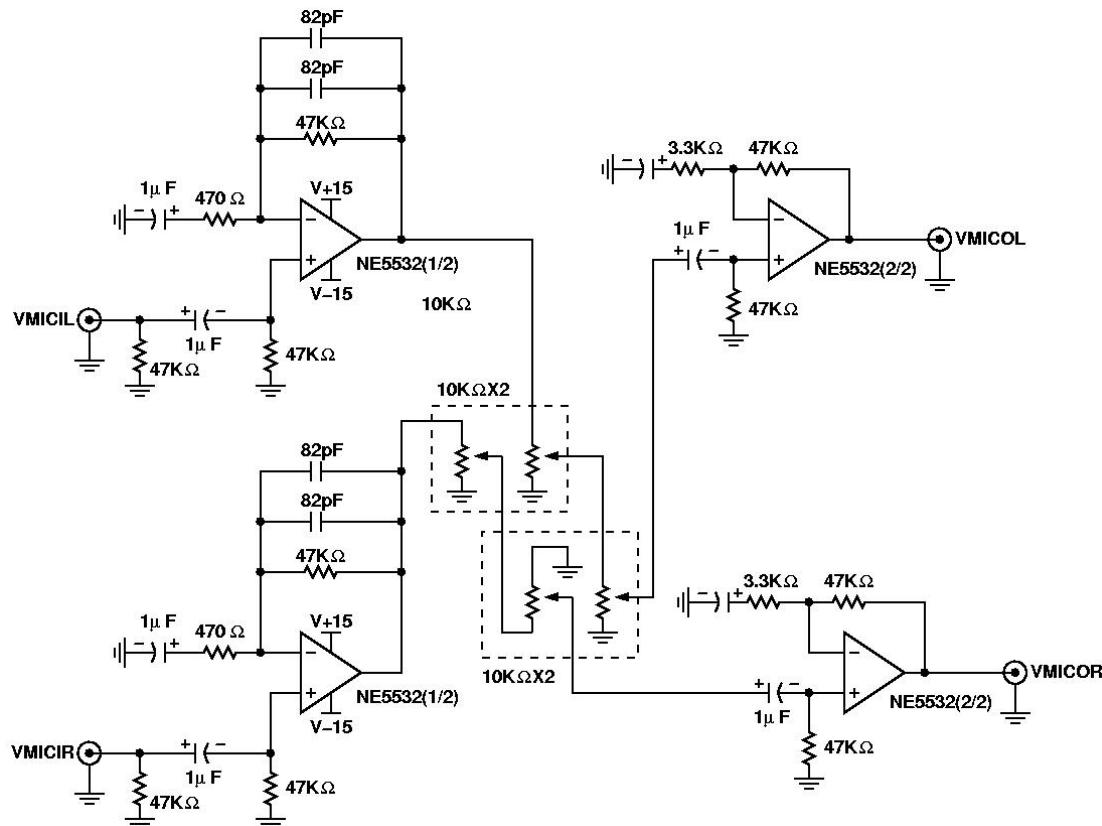

樣板電路如圖 Fig.3A.3 所示，放大器本體選用德州儀器的運算放大器(NE5532)，因為與其他放大器相比，具有相對較低的雜訊，以及在相同的頻寬下，此放大器消耗較少的功率。

Fig.3A.3. 可變增益放大器電路圖

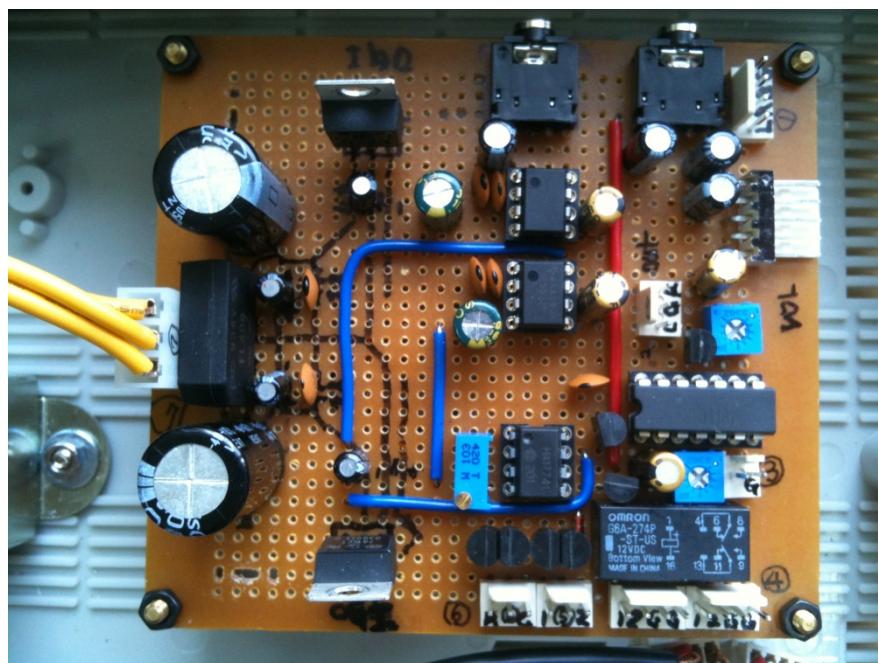

本電路接續麥克風的輸出端，而此放大器之輸入端為全差動節點(VMICIL、VMICIR)，經由接成非反向回授型式(Non-Inverting Configuration)之低雜訊放大器(NE5532)來放大，此級(1/2)的轉角頻率(Corner Frequency, -3dB Bandwidth)由回授之電阻和電容之時間常數決定，在本設計中約為20kHz。整體增益藉由改變第一級的負載電阻來控制，最後的輸出節點為(VMICOL、VMICOR)。電路的增益為40dB、整體可調整增益範圍為0.5dB~46dB、頻寬為16Hz~16kHz的前級放大電路。實作在印刷電路板(PCB Board)上的照片如Fig.3A.4所示。未來將以此電路之增益、頻寬及雜訊要求為參考，做為晶片設計的考量。

Fig.3A.4. 可變增益放大器樣板

#### 參考文獻

- [Deligoz 10] Deligoz, I.; Naqvi, S. R.; Copani, T.; Kiaei, S.; Bakkaloglu, B.; Je, S.-S.; Chae, J.; , "A MEMS-Based Power-Scalable Hearing Aid Analog Front End," *Biomedical Circuits and Systems, IEEE Transactions on* , vol.PP, no.99, pp.1, 0.

### 3B. 低功率 Delta-Sigma ADC

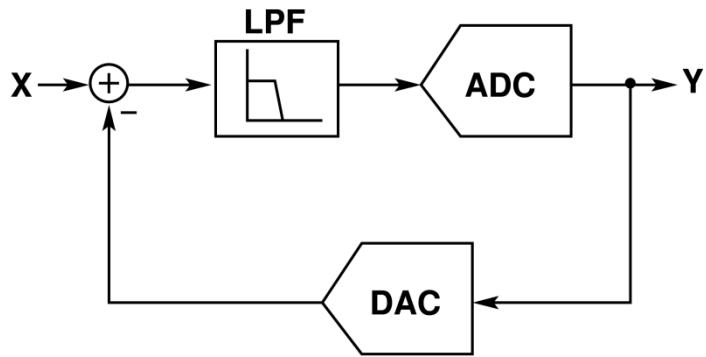

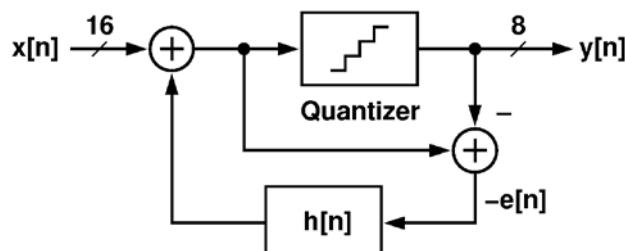

在助聽器電路中，需要使用高動態範圍(Dynamic Range)的類比數位轉換器，因此選擇音頻、高解析度的 Delta-Sigma Modulator 做為前端電路。此種電路架構如 Fig 3B.1，由類比濾波器(LPF)、類比數位轉換器(ADC)以及數位類比轉換器(DAC)所組成，形成一負回授之閉迴路而得到高解析度之數位訊號。因助聽器供應電源為電池，電壓僅有 1V，此類比電路需要挑戰在低電壓操作下，仍然維持高解析度，並在此條件下盡可能的減少功率消耗來完成。

Fig 3B.1: Delta-Sigma Modulator 架構

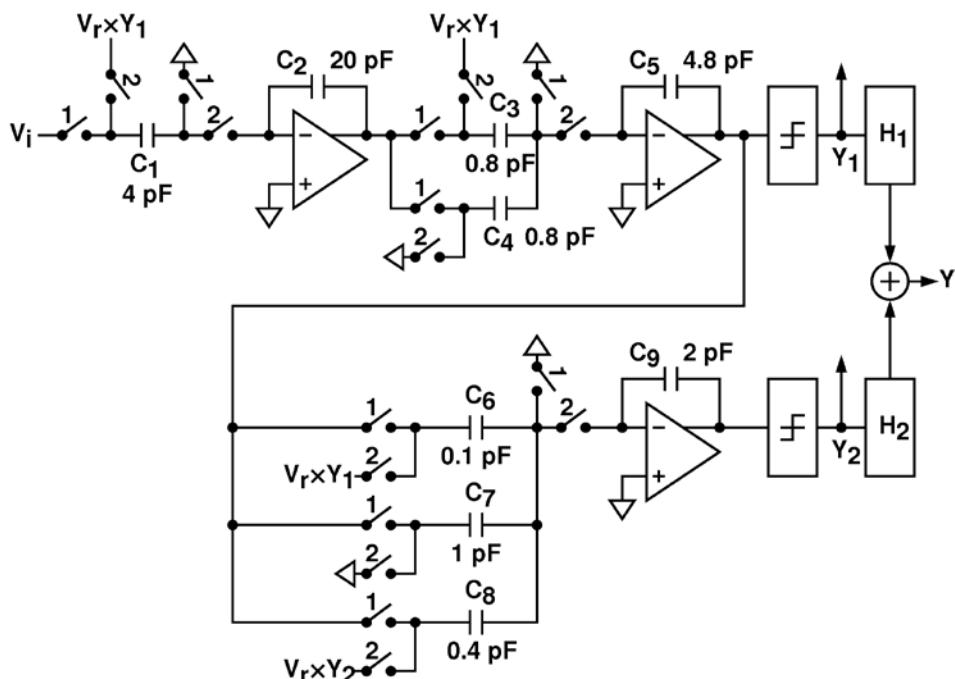

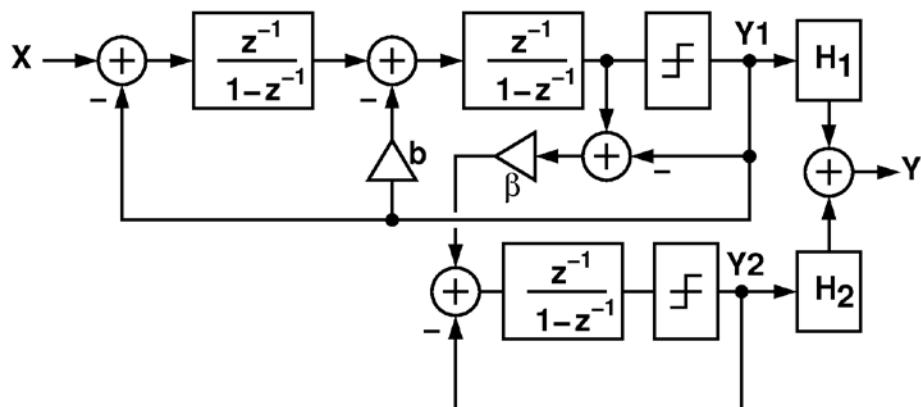

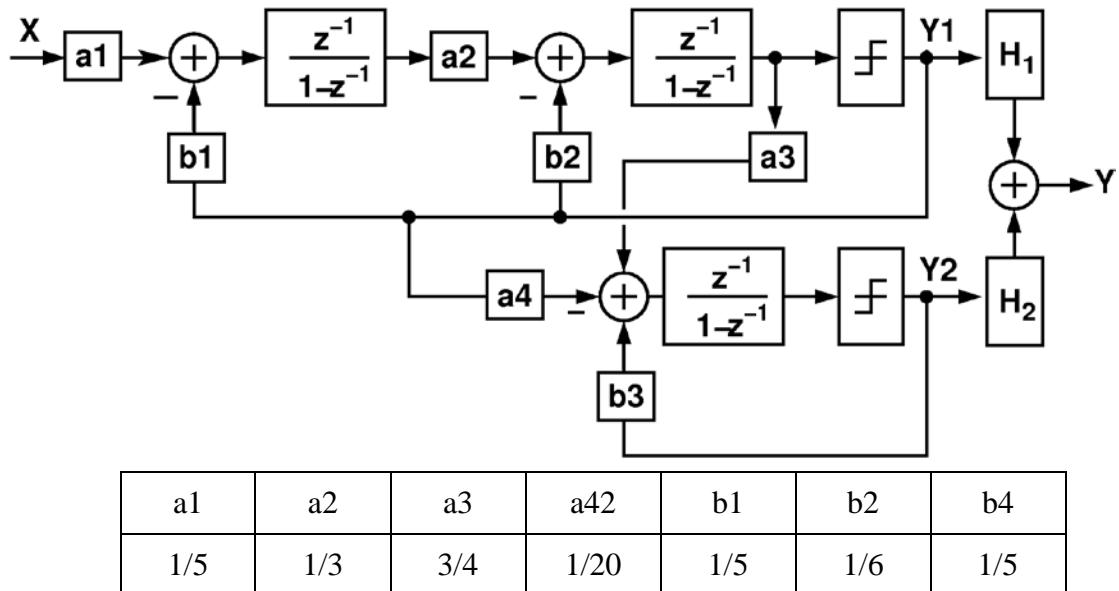

為了維持高解析度，本設計需要三階雜訊形變(Noise Shaping)。此種設計需要回授三階濾波器，十分容易產生閉迴路的不穩定而振盪。在此使用疊接組態(Multi-Stage Noise Shaping, MASH)來確保迴路穩定，架構如 Fig. 3B.2。輸入訊號 X 進入一個二階組態的閉迴路，並將此級的量化雜訊(Quantization Noise)送入一個一階組態的閉迴路。將二個迴路的數位輸出經過數位濾波器 H1 及 H2 處理後得到的 Y 將會是三階雜訊形變(3<sup>rd</sup>-order Noise Shaping)後的量化雜訊。本設計裡的量化器及其輸出，Y1 及 Y2，都只有一位元以確保系統的線性度。其中， $H_1 = z^{-1}$ ， $H_2 = (1/\beta)(1 - z^{-1})^2$ 。

Fig 3B.2: 2-1 MASH 架構

傳統的設計會令  $b=2$ ，而我們採用  $b=2.5$  來壓低可能會出現的 Spectral Tones。雖然此系統會有一個極點在  $z=-1$  處。但是在量化器的非線性操作下，本系統仍然可以維持穩定。另外， $\beta$ 係數也要小心選擇。因為 Y 裡的量化雜訊反比於  $\beta^2$ ，所以  $\beta$ 要大。但是大  $\beta$ 會增大第2迴路的輸入範圍，而必須提升第2迴路

的電路特性。我們選擇  $\beta = 0.25$ 。

如 Fig. 3B.3 所示，所有積分器的輸出範圍都經過調整。其中第一個積分器和第三個積分器的輸出訊號減小成原來的  $1/5$ ，而第二個積分器的輸出訊號減小成原來的  $1/15$ 。本設計在 Oversampling Ratio (OSR) 等於 128 時，其訊號對量化雜訊比可達 112 dB。

Fig 3B.3: 差積調變器架構

Fig 3B.4: 差積調變器電路

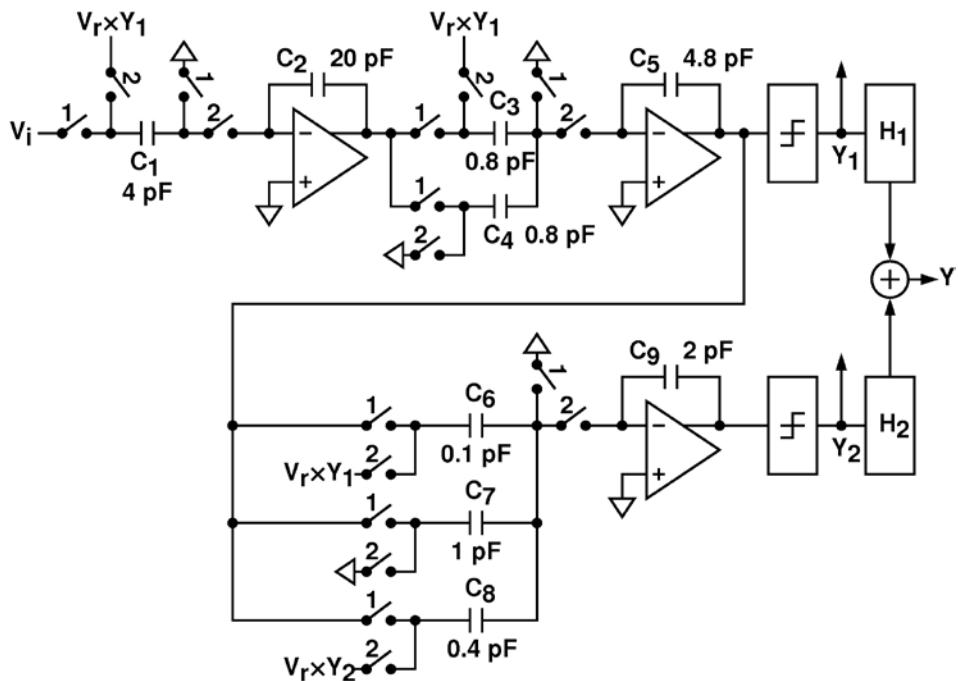

差積調變實作電路如 Fig 3B.4 所示。第一級的二階低通濾波器由二個運算放大器接成負回授形式，並以交換式電容(Switched-Capacitor)的方式來完成離散時間積分器(Discrete-Time Integrator)。此種型式的積分器的特色是極點僅與電容比

例相關，不需要在晶片完成後額外調整電容值。輸入電容考慮將熱雜訊最小化，因熱雜訊的方均根值與電容大小成反比，在計算雜訊底線(Noise Floor)後選擇了輸入電容  $C_1 = 4 \text{ pF}$ ，而為完成第一級的積分器係數選擇回授電容  $C_2 = 20 \text{ pF}$ 。第二級積分器的雜訊考量較第一級為寬鬆，經由計算選擇了輸入電容為  $C_3 = C_4 = 0.8 \text{ pF}$ ，回授電容為  $4.8 \text{ pF}$ 。第三級積分器的輸入訊號為量化雜訊，因此輸入電容的熱雜訊只要比量化雜訊小即可。經由計算可以得到第三級積分器的輸入電容為  $C_6 + C_7 + C_8 = 1.5 \text{ pF}$ ，回授電容  $C_9 = 2 \text{ pF}$ 。

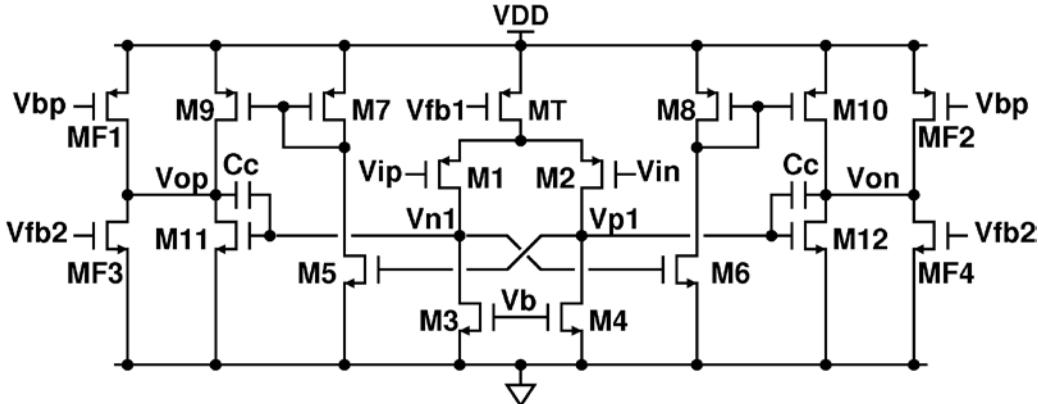

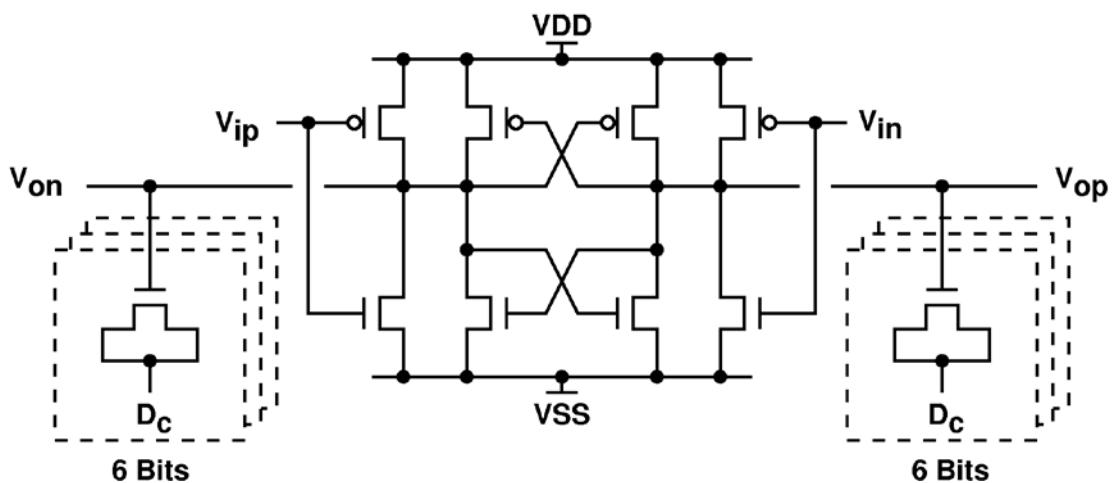

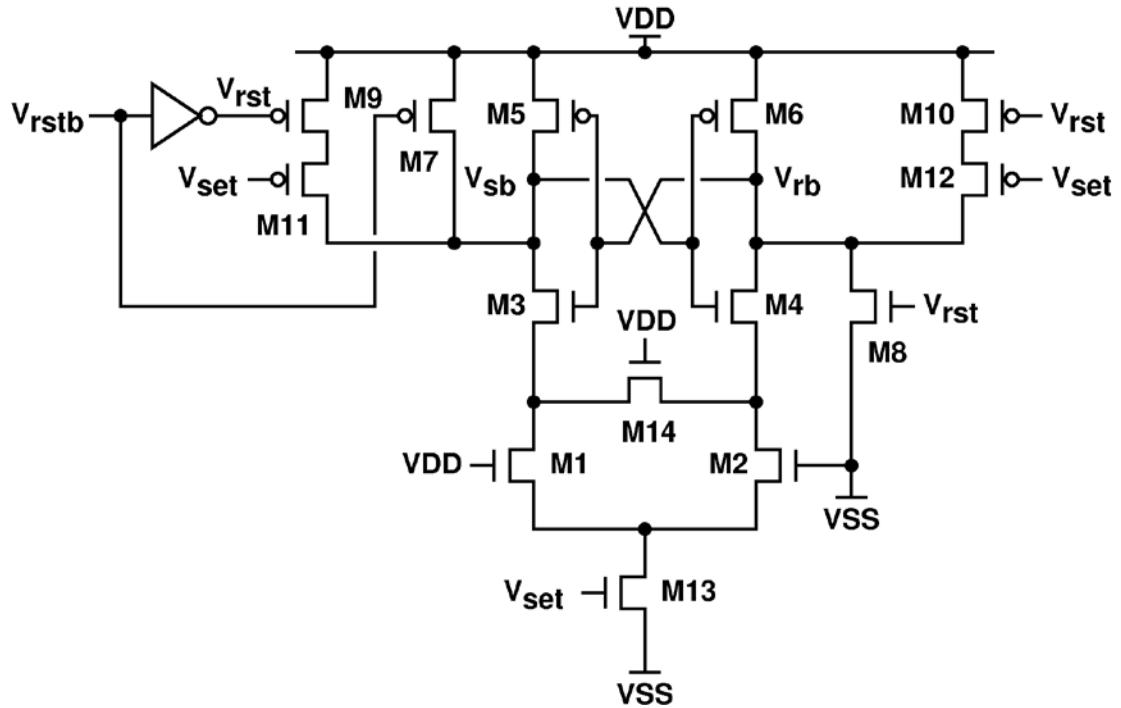

Fig 3B.5: 運算放大器電路

Fig 3B.6: 比較器電路

Fig 3B.5 是積分器使用的運算放大器的電路圖。此電路架構的輸入對為一源極耦合對(Source-coupled Pair)，具有共模拒斥(Common-Mode Rejection)的功用。考量閃爍雜訊對電路效能的影響，我們將 M1、M2 的寬長比選大，經由模擬驗證可以順利的將等效輸入雜訊符合要求。運算放大器的第二級採用 Class A/AB 的架構，期望在輸出點上拉和下拉的能力是一致的。此放大器使用兩組共模拒斥回授電路產生  $V_{fb1}$  及  $V_{fb2}$  電壓，分別來穩定輸入級與輸出級的共模電壓。放大器有 74 dB 的電壓增益。為了減少功率損耗，上述之運算放大器會依據積分器的需求而以等比例調整寬長比。

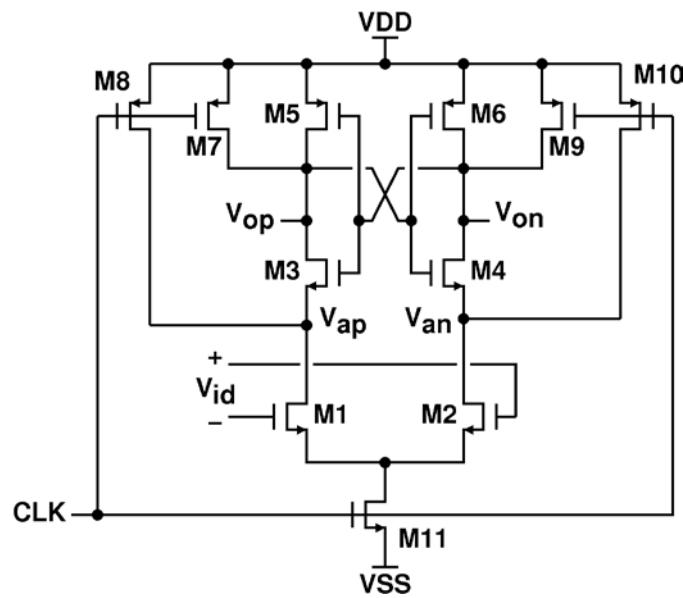

Fig 3B.6 是差積調變器使用的比較器的電路圖。這是一個 Latch 式的比較器。當 CLK 在低電壓時，電路處於 Reset 狀態，電晶體 M1 至 M6 的 Drain 端都被拉到 VDD。當 CLK 從低電壓拉到高電壓，差動輸入  $V_{id}$  首先經由 M1 和 M2 放大，再經由 M3 – M6 產生 Regeneration。

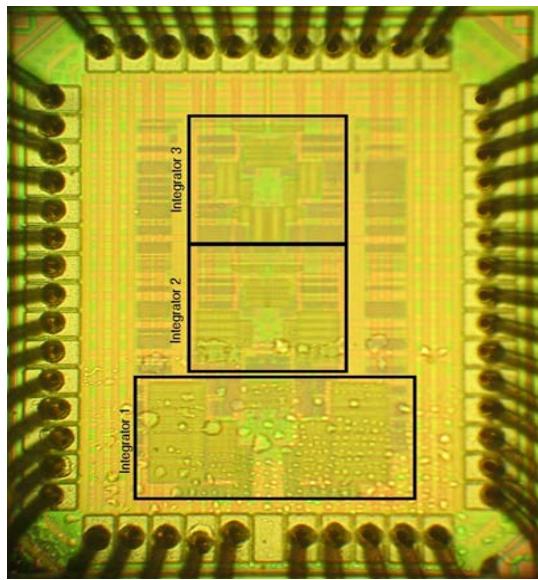

Fig 3B.7 DSM 晶片照片。

|                    |                              |

|--------------------|------------------------------|

| Technology         | 90 nm CMOS                   |

| Signal Bandwidth   | 24.4 kHz                     |

| Sampling Rate      | 6.25 MHz                     |

| Oversampling Ratio | 128                          |

| Input Range        | 500 mVpp                     |

| Peak SNDR (dB)     | 88                           |

| Dynamic Range      | 100 dB                       |

| SFDR (dB)          | 99                           |

| Supply Voltage     | 1.0 V                        |

| Power Dissipation  | 860 $\mu$ W                  |

| Active Area        | 560x780 $\mu$ m <sup>2</sup> |

Table 3B.1

以上設計的差積調變器(DSM)已經用 TSMC 90 nm CMOS 製程製作成晶片。Fig 3B.7 是晶片照片。DSM 占用的面積為  $560 \times 780 \mu\text{m}^2$ 。在 1 V 的電壓下操作，DSM 的操作頻率可達 6.25 MHz，而只消耗 860  $\mu$ W 的功率。假設 Oversampling Ratio 是 128，則 DSM 的輸入頻寬為 24.4 kHz。DSM 的差動輸入範圍是  $\pm 800 \text{ mV}$ 。

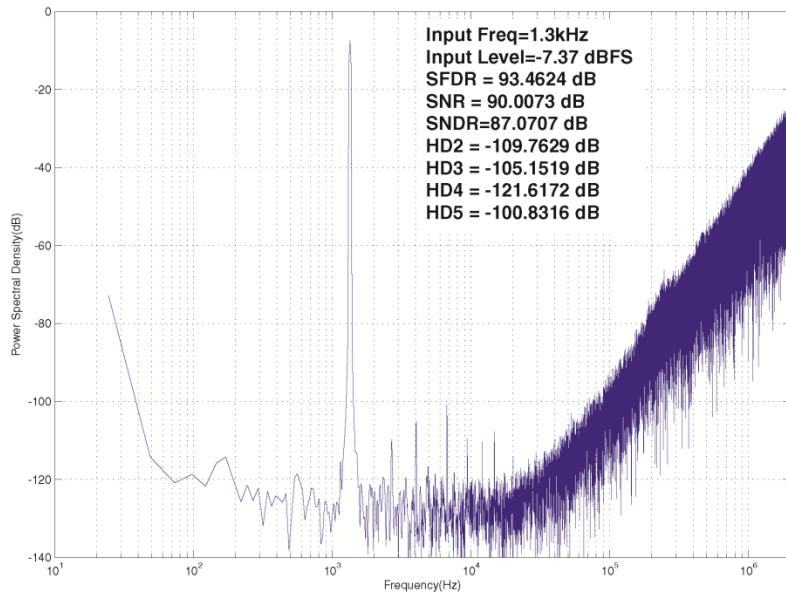

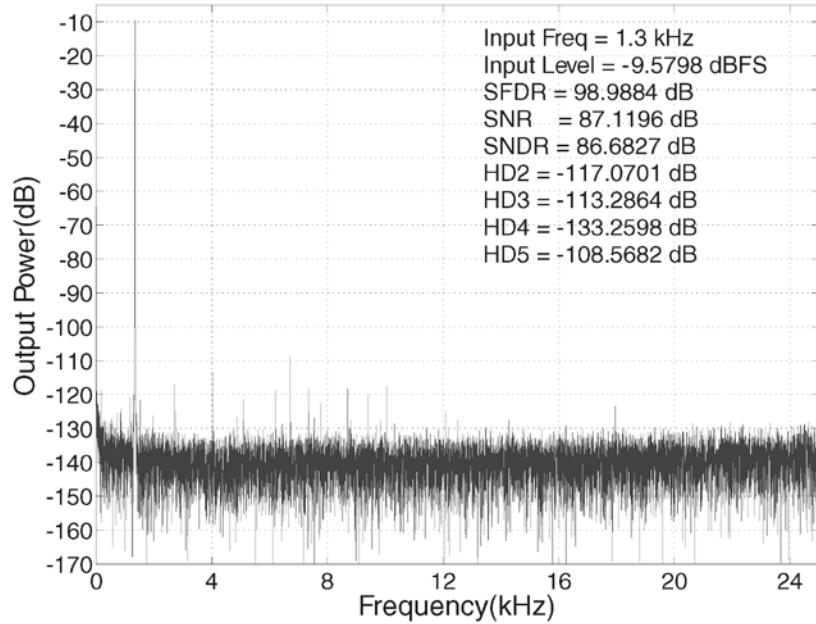

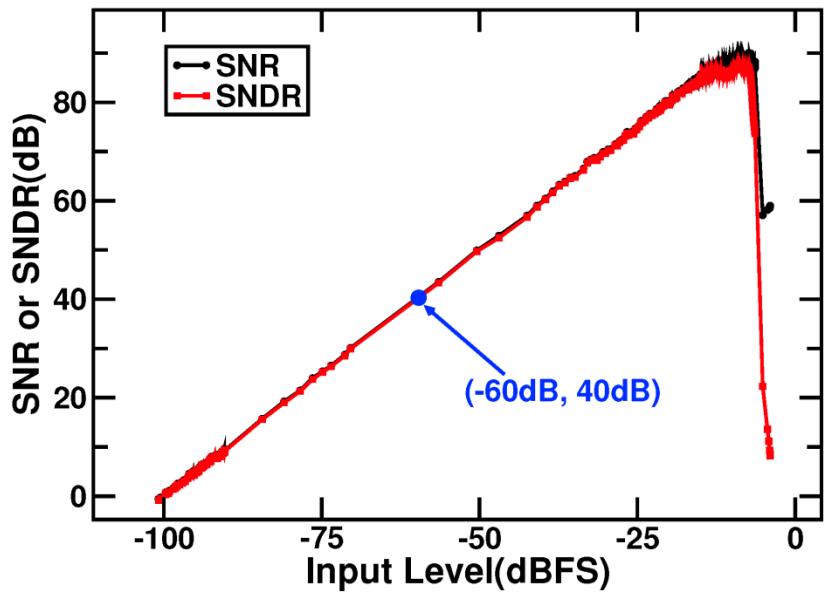

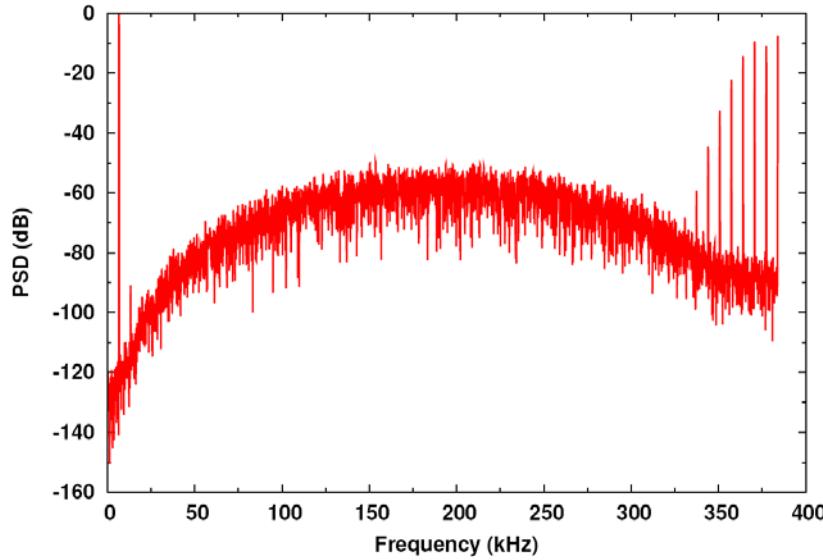

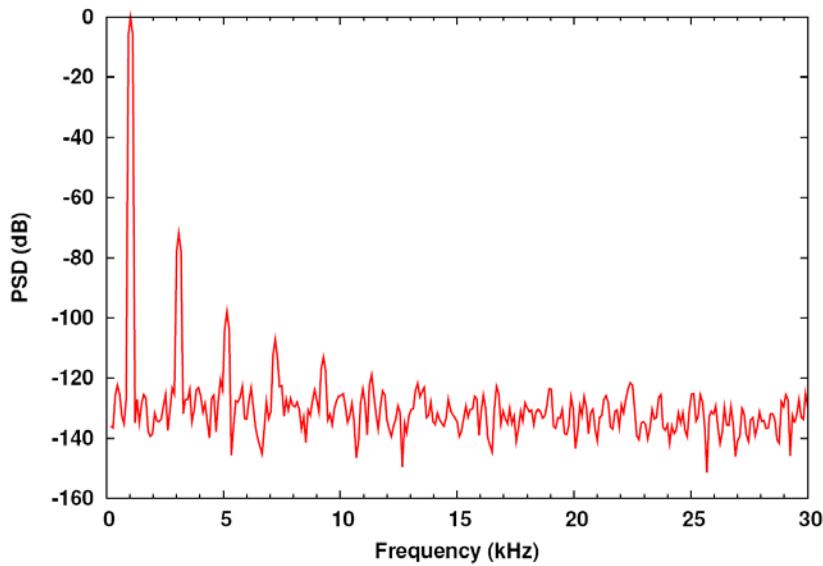

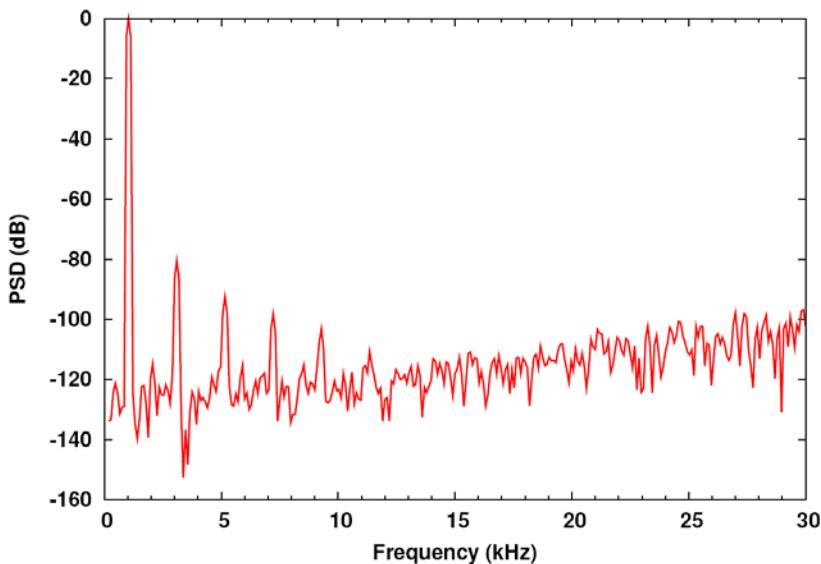

Fig 3B.8 是量測到的全頻 DMS 輸出頻譜。輸入訊號的頻率是 1.3 kHz，輸入振幅是 -7.37 dBFS。Fig 3B.9 是量測到的基頻 DMS 輸出頻譜。Signal-to-Noise Ratio (SNR) 有 90 dB，Signal-to-Noise-Plus-Distortion ratio (SNDR) 有 88 dB，Spurious-Free Dynamic Range (SFDR) 有 99 dB，Total Harmonic Distortion Plus Noise (THD+N) 有 -93 dB。Fig 3B.10 是量測到的 SNR/SNDR/SFDR 對輸入訊號振幅的關係圖。輸入的頻率是 1 kHz。最大的 SNR/SNDR/SFDR 全發生於輸入訊號振幅是 -7.37 dBFS 時。Dynamic Range 則有 100 dB。Table 3B.1 是晶片量測到的規格。

Fig 3B.8: 量測到的全頻 DMS 輸出頻譜。

Fig 3B.9: 量測到的基頻 DMS 輸出頻譜。

Fig 3B.10: 量測到的 SNR/SNDR 對輸入訊號振幅的關係。輸入的頻率是 1 kHz。

### 參考文獻

- [Shahriar97] Shahriar Rabii and Bruce A. Wooley, "A 1.8-V Digital-Audio Sigma-Delta Modulator in 0.8- $\mu$ m CMOS," *IEEE J. Solid-State Circuits*, vol. SC-32, pp. 783-796, June 1997.

- [Murmann06] Boris Murmann et al., "Impact of Scaling on Analog Performance and Associated Modeling Needs," in *IEEE Transactions on Electron Devices*, vol. 53, pp. 2160-2316, Sep. 2006.

- [Chang13] C-L Chang and J-T Wu, "A 1-V 100-dB Dynamic Range 24.4-kHz Bandwidth Delta-Sigma Modulator," 2013 IEEE International Symposium on Circuits and Systems, pp. 813-816, May 2013.

### 3C. 數位 Class-D 喇叭驅動電路

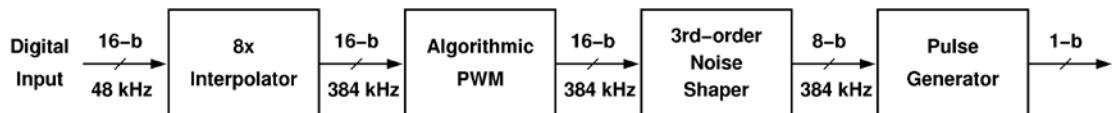

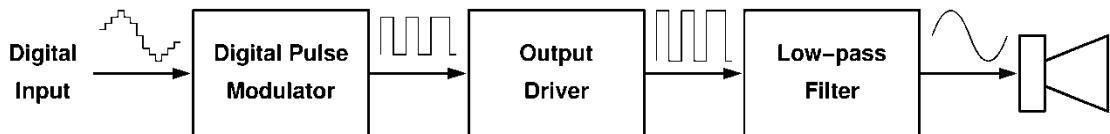

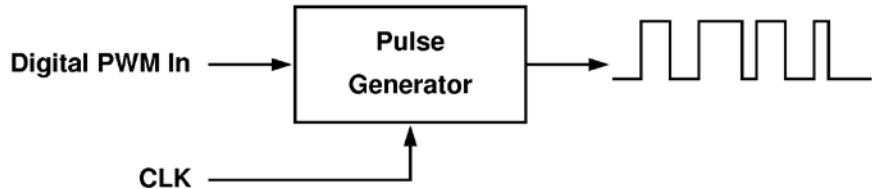

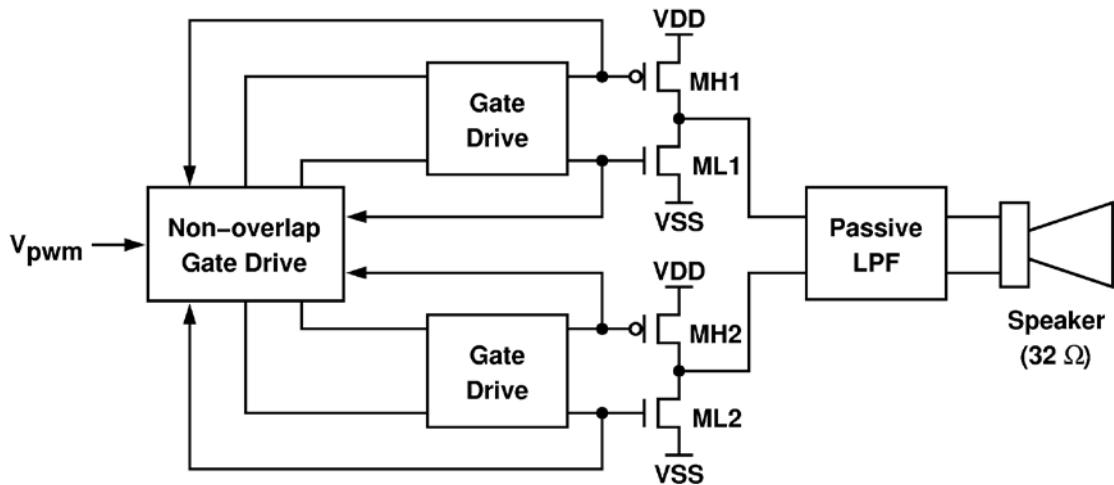

助聽器中的喇叭驅動電路必須具備高效率和低失真。圖 3C.1 為數位 Class-D 放大器之架構圖，Class-D 放大器採用開關切換方式進行訊號調變與功率轉換。與線性放大器比較，它具有較高的轉換效率，適合應用於低功率系統。而數位 Class-D 放大器架構可直接接收前級助聽器計算引擎的輸出訊號，不須經由數位/類比轉換器轉換，更具有省電的優勢。數位 Class-D 放大器可分為兩個區塊：訊號調變電路（Digital Pulse Modulator）和輸出級電路（Output Driver）。訊號調變電路的作用是對前級數位電路的輸出訊號作調變，將其轉換成一位元的脈衝（Pulse）訊號來控制輸出級電路的開關電晶體。輸出級電路基本上是一連串的緩衝器和開關電晶體，提供驅動微機電喇叭所需的電流。接在輸出級電路之後的低通濾波器（Low-pass Filter）作為解調變用，將一位元的脈衝訊號還原成類比的音頻訊號。

Fig 3C.1: 數位 Class-D 放大器。

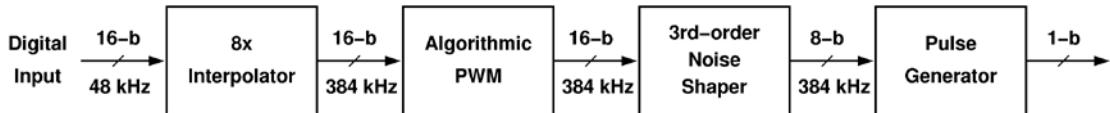

Fig 3C.2: 數位 PWM 調變器。

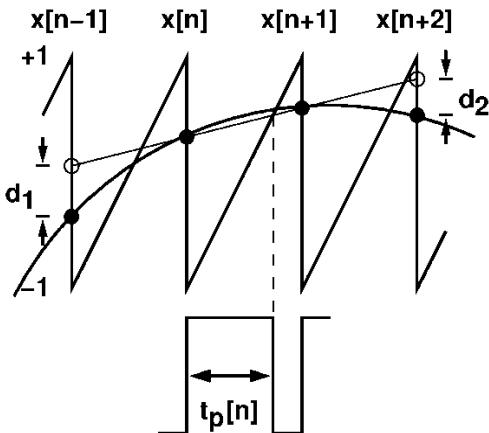

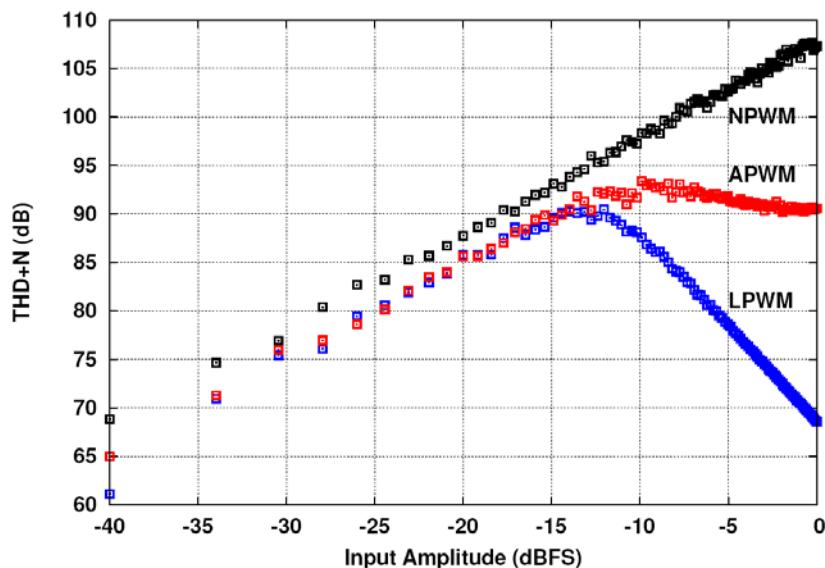

目前已發表應用於助聽器之數位 Class-D 放大器依照訊號調變方式可分為 Delta-Sigma Modulation (DSM) [Kim06] 和 Pulse-Width Modulation (PWM) [Adrian09] 兩類。其中 PWM Class-D 驅動電路的切換頻率低，理論上會有最高的轉換效率，適合實現助聽器應用的數位 Class-D 放大器。圖 3C.2 所示為我們設計的數位 PWM 調變器區塊圖。此調變器的數位音頻輸入訊號（16 位元、取樣頻率 48 kHz）首先會經過 8 倍的內插（Interpolation）轉換成 16 位元、384 kHz 的訊號，內插的目的除了提高取樣點以增進數位 PWM 電路（Algorithmic PWM, APWM）之總諧波失真（Total Harmonic Distortion, THD）表現外，並提供後面進行雜訊形變（3<sup>rd</sup>-order Noise Shaper）所需的超取樣（Over-Sampling）。內插後的聲音訊號接著透過 APWM 區塊電路調變為 16 位元、384 kHz 的數位脈衝寬度訊號。圖 3C.3 為 APWM 調變方法之示意圖[Pascual00]，圖中  $t_p[n]$  為利用輸入訊號  $x[n-1]$ 、 $x[n]$ 、 $x[n+1]$  和  $x[n+2]$  所求得的脈衝寬度訊號，圖 3C.4 是以 6.6 kHz 單頻訊號輸入（16 位元，384 kHz）的 APWM 總諧波失真加雜訊（THD+N）模擬結果，其中 NPWM 為理想的 16 位元 PWM 訊號之 THD+N 表現、LPWM 為僅利用  $x[n]$  和  $x[n+1]$  作線性內差所得 PWM 訊號之 THD+N 表現。由此圖可看出 APWM 可改善 LPWM 的 THD+N 表現隨著輸入振幅增加而惡化的現象，在輸入訊號振幅為 0 dBFS 時，APWM 的 THD+N 為 -91 dB。

Fig 3C.3: APWM (Algorithmic PWM) 調變方法。

Fig 3C.4: APWM 總諧波失真加雜訊圖。

Fig 3C.5: Noise Shaper。

在 APWM 區塊之後，藉由三階 Noise Shaper，16 位元的數位脈衝寬度訊號將轉為 8 位元、384 kHz，以便能在不損失訊號精確度的前提下大幅降低 Pulse Generator 的時脈頻率，降低電路的功率消耗。圖 3C.5 所示為 Noise Shaper 之架構圖，其中  $h[n]$  為回授濾波器的脈衝響應(impulse response)。圖 3C.6 是以 6.6 kHz 單頻輸入(16 位元, 384 kHz)的 APWM + 3<sup>rd</sup>-order Noise Shaper 輸出訊號頻譜圖，其 THD+N、THD 和 SNR 分別為 -89 dB、-92 dB 和 96 dB。此 Noise Shaper 透過 3 階的回授濾波器，可將 8 位元的 PWM 訊號之音頻頻段雜訊比維持在 95 dB 左右，此系統在高輸入訊號頻率下的 THD+N 表現則是被 APWM 的非線性失真所

決定。表 3C.1 所列為 APWM + 3<sup>rd</sup>-order Noise Shaper 之 THD+N、THD 和 SNR 的表現。

Fig 3C.6: APWM + Noise Shaper 頻譜圖。

Table 3C.1: APWM + 3<sup>rd</sup>-order Noise Shaper 表現。

| Input Frequency | THD+N (dB) | THD (dB) | SNR (dB) |

|-----------------|------------|----------|----------|

| 1.03 kHz        | -95.1      | -106.4   | 96.3     |

| 6.66 kHz        | -89.5      | -92.2    | 96.4     |

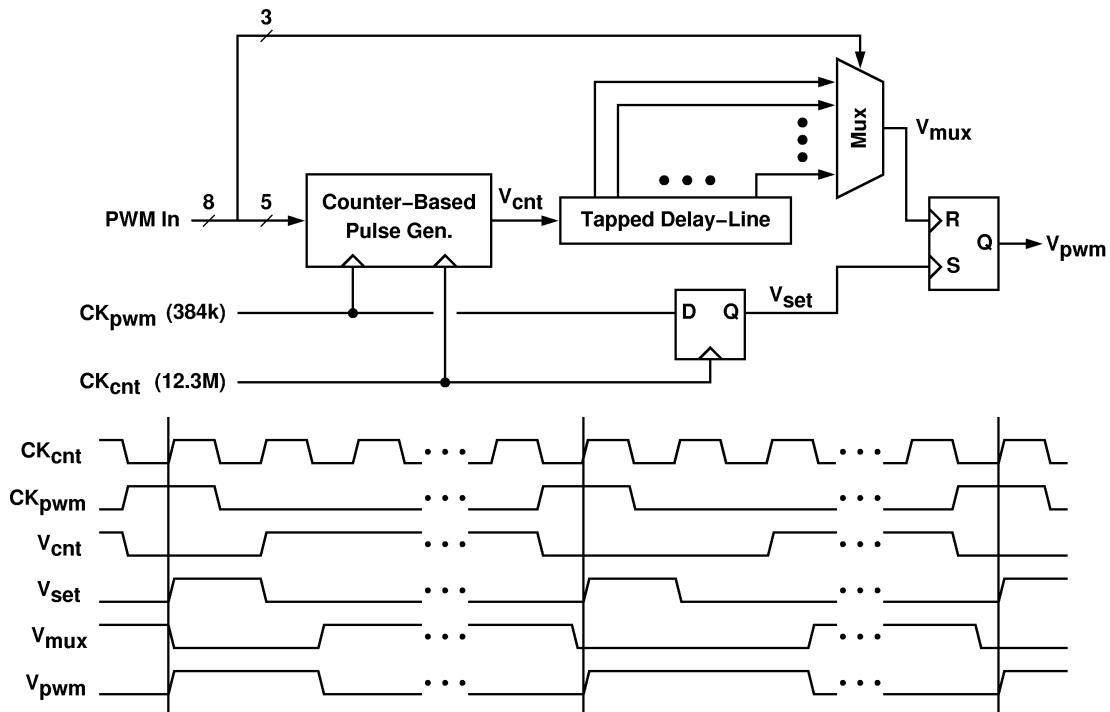

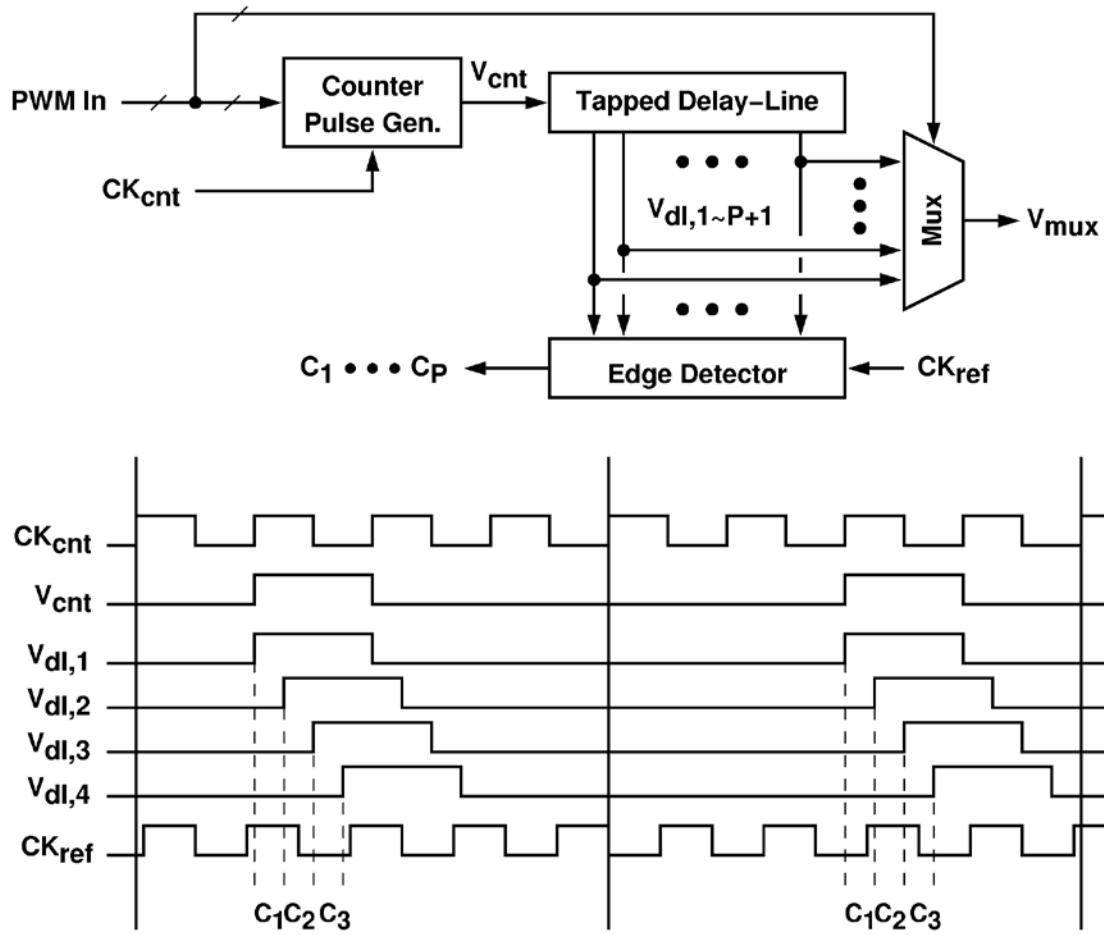

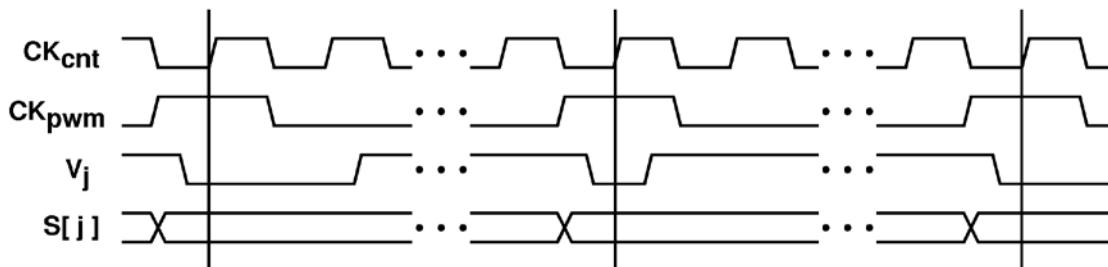

最後 Noise Shaper 輸出端的 8 位元脈衝寬度訊號將經由 Pulse Generator 產生 1 位元的 PWM 訊號，圖 3C.7 為 Pulse Generator 之示意圖，其輸入訊號為代表脈衝寬度的數位訊號，輸出訊號為在一 PWM 週期內寬度與輸入相對應的脈衝。數位 PWM 調變器中 Pulse Generator 常見的實現方法有：(1) 以數位計數器(Counter)實現；(2) 以延遲線 (Tapped Delay-Line) 實現；(3) 混合計數器與延遲線方式實現。用計數器來實現 Pulse Generator 需要一高頻時脈，數位計數器的操作頻率是輸入訊號取樣頻率的 2<sup>8</sup>倍，在此為 98.3 MHz。高操作頻率導致較高的功率消耗，使得此架構較不適合應用於超低功率的系統。利用延遲線產生不同的脈衝寬度訊號實現 Pulse Generator 可免除高頻時脈的需求，但每個延遲單元 (delay-cell) 所產生的延遲時間準確度直接影響到輸出訊號的 SNR 表現，以此系統的 SNR 規格 (>90 dB) 而言，要在一個 PWM 週期內產生所需精確度的 2<sup>8</sup>個延遲時間是不易達到的。混合計數器與延遲線的方法可降低計數器的操作頻率和減少延遲單元數目以簡化延遲線的設計，適合用於低功率數位 PWM 系統中。圖 3C.8 為此混合型 Pulse Generator 之架構圖和波形示意圖，在 8 位元的輸入訊號 (PWM In) 中，前 5 個 MSB (Most Significant Bit) 由計數器 (Counter-Based Pulse Gen.) 處理產生相對應的脈衝寬度訊號 ( $V_{cnt}$ )，此訊號根據輸入的 MSB 在其相對應的計

數器時脈 ( $CK_{cnt}$ ) 升緣設置為 1，且在每個 PWM 週期時脈 ( $CK_{pwm}$ ) 升緣重置為 0。 $V_{cnt}$  接著送進延遲線 (Tapped Delay-Line)，在一個  $CK_{cnt}$  週期內產生 8 個等分的脈衝訊號，再根據 PWM In 的 3 個 LSB (Least Significant Bit) 透過多工器 (Mux) 選擇出 PWM 重置 (reset) 訊號 ( $V_{mux}$ )，而 PWM 設置 (set) 訊號 ( $V_{set}$ ) 是由 PWM 週期時脈透過計數器時脈同步化 (synchronize) 產生。最後 PWM 調變輸出訊號 ( $V_{pwm}$ ) 則是根據  $V_{set}$  和  $V_{mux}$  由 SR flip-flop 產生。

Fig 3C.7: Pulse Generator。

Fig 3C.8: 混合型 Pulse Generator 架構及波形圖。

Fig 3C.9: 延遲線時間歪斜偵測架構及示意圖。

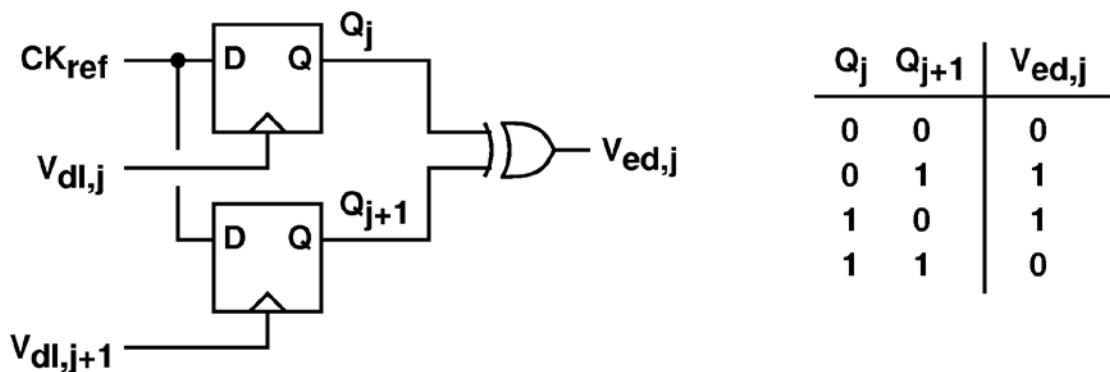

在圖 3C.8 架構中，延遲線的總延遲時間必須與一個  $CK_{cnt}$  的週期相同，這點可以運用延遲鎖相迴路 (Delay Lock Loop, DLL) 技術來克服。另外延遲線中 8 個延遲單元的延遲時間也必須相同，延遲單元之間的時間歪斜 (Timing Skew) 將會影響到此系統的 SNR 表現。為了解決此問題，我們提出了一校正延遲線時間歪斜的技術。圖 3C.9 所示為偵測延遲線時間歪斜的架構圖和示意圖，圖中  $CK_{ref}$  是一個與  $CK_{cnt}$  非同步的時脈訊號，利用邊緣偵測器 (Edge Detector) 來偵測  $CK_{ref}$  升緣 (Rising Edge) 發生的時間，並將其落在每個延遲單元區間內的次數分別以  $C_1, \dots, C_P$  紀錄下來。圖 3C.9 下方為此偵測方法以 4 位元輸入 (2-bits counter + 2-bits delay-line) 為例所畫的波形示意圖，根據 2 位元 MSB，計數器的輸出 ( $V_{cnt}$ ) 為其相對應的寬度訊號，延遲線則將計數器輸出延遲不同時間，產生出每個脈衝寬度訊號 ( $V_{dl,1 \sim 4}$ )， $C_1, C_2, C_3$  紀錄著  $CK_{ref}$  升緣在每兩個相鄰的延遲線輸出之間發生的次數。由於  $CK_{ref}$  與  $CK_{cnt}$  非同步， $CK_{ref}$  升緣發生時間的機率密度 (probability density) 會呈現均勻分布 (uniform distribution)，若每個延遲單元間沒有時間歪斜， $CK_{ref}$  升緣在每兩個相鄰的延遲線輸出之間的發生次數會相同，因此我們可以藉由  $C_1$  到  $C_P$  的值得到延遲線時間歪斜的資訊。

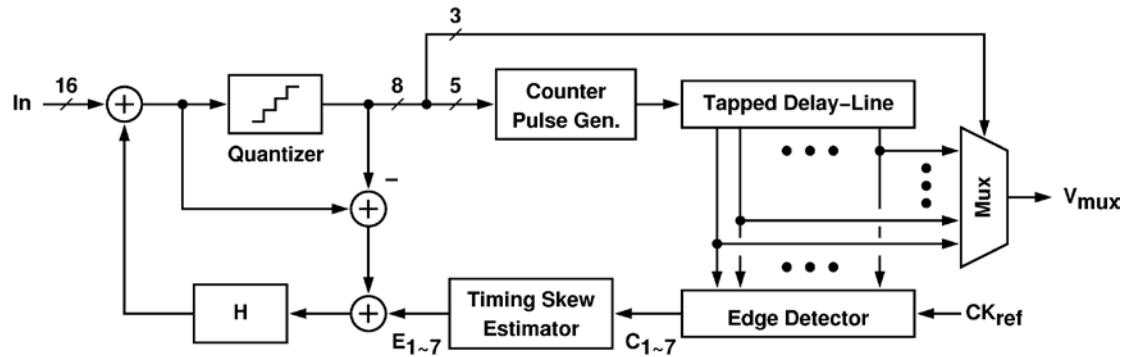

Fig 3C.10: 具延遲線時間歪斜校正之混合型 Pulse Generator。

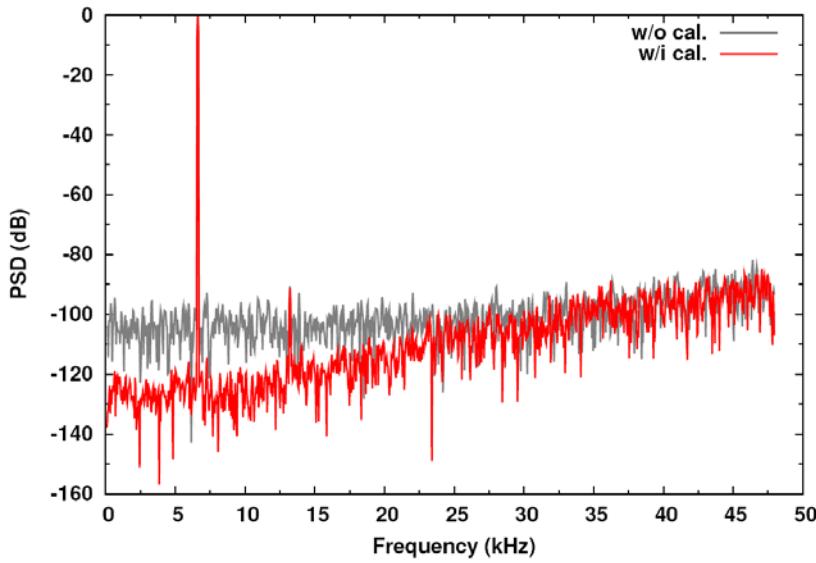

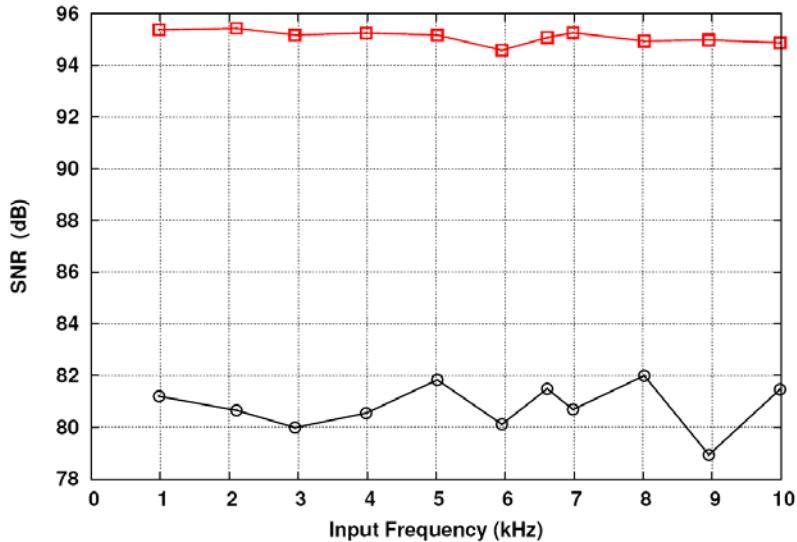

在取得延遲線時間歪斜資訊後，我們可以利用此資訊校正延遲線的時間歪斜，補償此效應對系統造成的 SNR 下降。圖 3C.10 為一具延遲線時間歪斜校正之混合型 Pulse Generator 的架構圖，時間歪斜校正器（Timing Skew Estimator）接收前述延遲線時間歪斜資料  $C_1, \dots, C_7$ ，並利用這些資料換算出每個延遲線時間歪斜相對應的數位脈衝寬度誤差量值。校正器所算得的誤差值將根據 Pulse Generator 的輸入訊號輸出給前級的 Noise Shaper，加進 Noise Shaper 中的量化誤差訊號，一併送至回授濾波器作誤差回授（Error Feedback）。圖 3C.11 為運用此延遲線時間歪斜校正技術之頻譜圖，由圖中灰色曲線（w/o cal.）可看出延遲線時間歪斜會導致輸出訊號音頻頻段內的雜訊準位（noise flow）上升，降低 SNR 表現。運用時間歪斜校正技術（紅色曲線，w/i cal.），雜訊準位可壓抑至接近理想延遲線的位準，補償此非理想效應。圖 3C.12 為 SNR 對輸入頻率的作圖，當時間歪斜校正沒有開啟時（黑色曲線）SNR 約為 81 dB，運用此校正技術後（紅色曲線），SNR 表現可提升至 94 dB。

Fig 3C.11: 延遲線時間歪斜校正頻譜圖。

Fig 3C.12: 延遲線時間歪斜校正 SNR 表現。

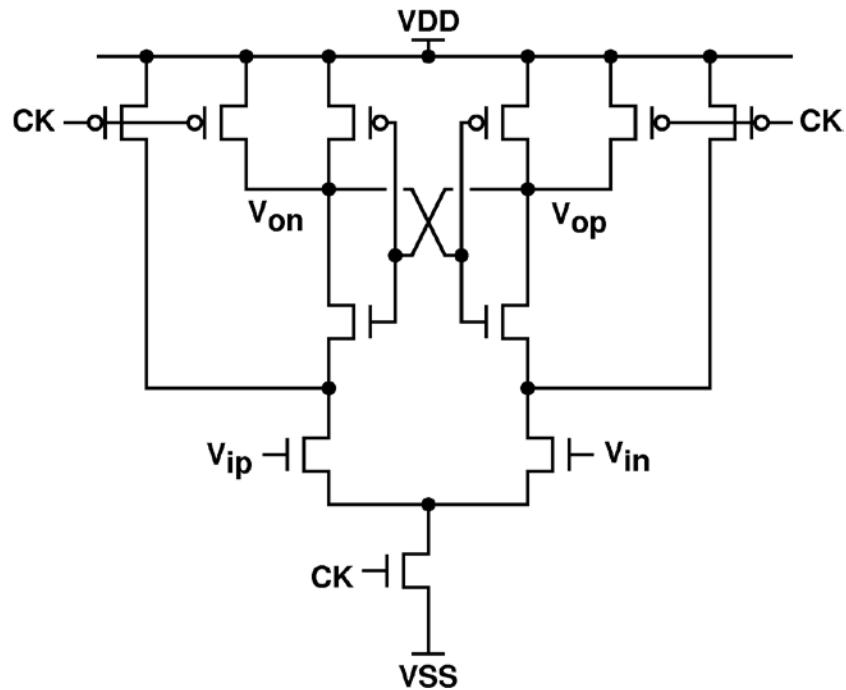

在此混合型 Pulse Generator 中（圖 3C.8、3C.9），Counter-Based Pulse Gen. 為一 5 位元數位計數器，由數位合成實現。Tapped Delay-Line、Mux、SR flip-flop 和 Edge Detector 均為類比區塊電路，將分述在以下各段。

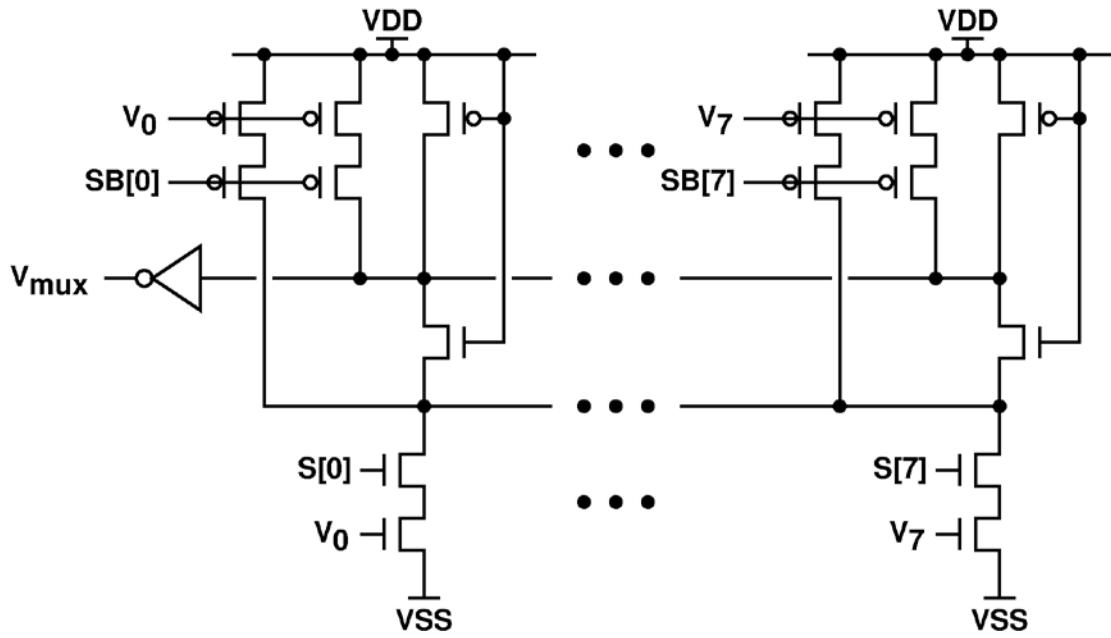

Tapped Delay-Line 由 8 個相同的延遲單元（delay cell）串接組成，圖 3C.13 為一 delay cell 的電路圖。藉由數位控制訊號  $D_C$  調整輸出端 ( $V_{op}$ 、 $V_{on}$ ) 的並聯電容，可控制 delay cell 的延遲時間，將 Tapped Delay-Line 的總延遲時間調整至約為一個  $CK_{cnt}$  的週期。這些並聯電容是利用具二進制權重（binary-weighted）面積大小的 MOS 電晶體來實現，並將其連接至 6 位元的數位控制訊號。控制電容又分為兩組（coarse 和 fine），分別用來粗調和微調 delay cell 的延遲時間。表 3C.2 所列為此數位控制 delay cell 的模擬結果，在此一個  $CK_{cnt}$  週期設計為 81.38 ns。在各種不同的製程 corner 和操作溫度下，delay cell 最大和最小延遲時間偏移分別為 +2.42 ns 和 -2.07 ns，coarse control 的調整範圍可覆蓋製程的飄移範圍。在初始時 coarse control 將先調整 delay cell 的延遲時間並固定其控制訊號，接著 fine control 對延遲時間作動態調整，在電路工作時將 Tapped Delay-Line 和  $CK_{cnt}$  的時間誤差維持在一定的範圍內。

Fig 3C.13: 數位控制 delay cell。

Table 3C.2: 數位控制 delay cell 模擬結果。

|                           |                         |

|---------------------------|-------------------------|

| Delay (Min, Typ, Max)     | (8.10, 10.17, 12.59) ns |

| Coarse control range      | $\pm 3.88$ ns           |

| Coarse control resolution | 127 ps                  |

| Fine control range        | $\pm 0.30$ ns           |

| Fine control resolution   | 10 ps                   |

Mux 電路要根據 PWM In 的 3 個 LSB，從 8 個具有不同延遲時間的輸入訊號選出一個來 ( $V_{\text{mux}}$ )，作為 PWM 調變脈衝的 reset 訊號。圖 3C.14 為 Mux 電路的相關訊號波形圖， $V_j$  ( $j=0 \sim 7$ ) 為 Mux 的輸入訊號，在每個 PWM 週期內， $V_j$  會在不同的  $CK_{\text{cnt}}$  升緣延遲一段時間 ( $t_{d,j}$ ) 後設置為 1，而在  $CK_{\text{pwm}}$  升緣同樣延遲  $t_{d,j}$  後重設為 0。 $S[j]$  為 3 位元 LSB 相對應溫度計碼 (thermometer code) 的第  $j$  個位元，在每個  $CK_{\text{pwm}}$  升緣轉態。根據輸入訊號的特性，此 Mux 可由圖 3C.15 電路來實現，圖中  $SB[j]$  為  $S[j]$  的反相訊號，此電路  $V_0 \sim V_7$  到  $V_{\text{mux}}$  延遲時間的不匹配 (mismatch) 模擬結果可達到 5 ps 以下。

Fig 3C.14: Mux 波形圖。

Fig 3C.15: Mux 電路圖。

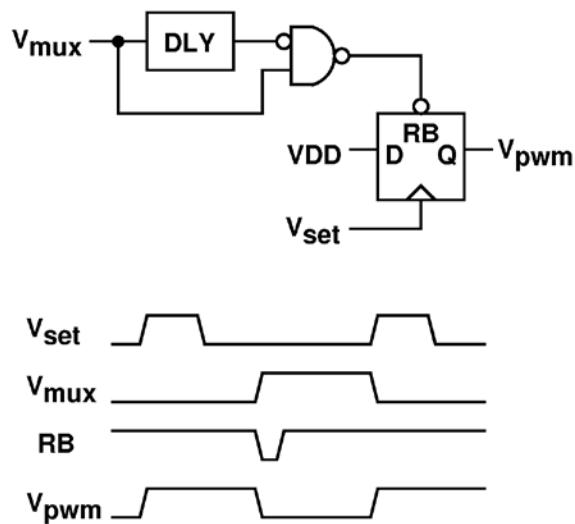

SR flip-flop 電路分別接收  $V_{set}$  和  $V_{mux}$  作為 set 和 reset 訊號產生  $V_{pwm}$ ， $V_{pwm}$  訊號必須在  $V_{set}$  升緣由  $VSS$  電壓變為  $VDD$  電壓，且在  $V_{mux}$  升緣由  $VDD$  變為  $VSS$ 。圖 3C.16 為其電路示意圖，將  $V_{set}$  接至一 D flip-flop 的 clock 觸發端並將其 data 輸入接到  $VDD$  便可達到 set 的功能。reset 的功能則是將  $V_{mux}$  經過一段時間延遲(DLY)後，利用 NAND 閘產生一短脈衝訊號(RB)來 reset 此 D flip-flop。此 D flip-flop 採用 Sense-Amplifier 的架構來實現，圖 3C.17 為此 D flip-flop Sense-Amplifier 的電路圖，將  $V_{sb}$  和  $V_{rb}$  接至一 static SR flip-flop 便完成 D flip-flop 電路。

Fig 3C.16: SR flip-flop 電路示意圖。

Fig 3C.17: D flip-flop Sense-Amplifier 電路圖。

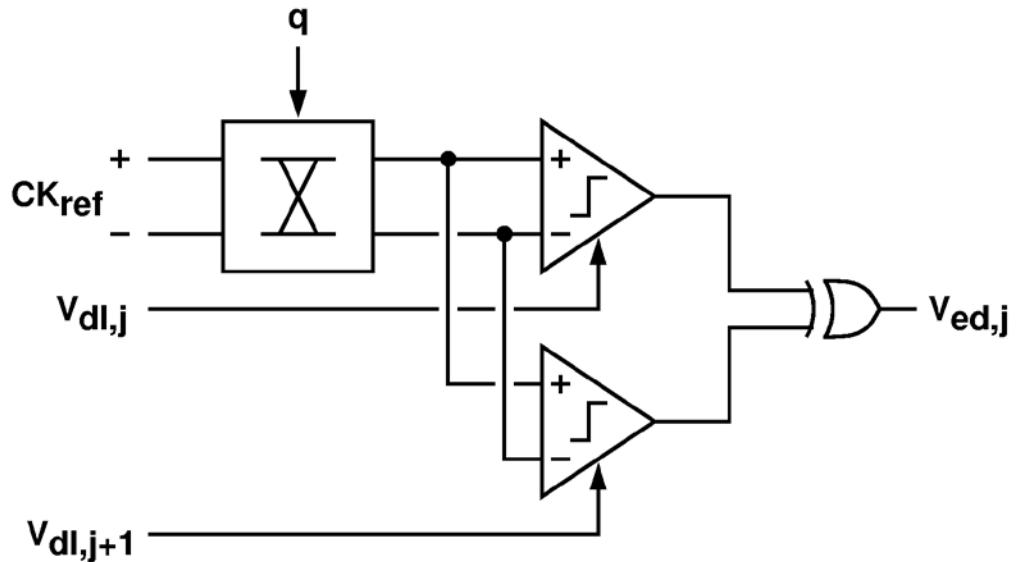

Edge Detector 的功用是偵測  $CK_{ref}$  在每個 delay cell 區間內發生轉態的事件，再送給 Timing Skew Estimator 統計並計算出每個延遲時間的誤差。圖 3C.18 為 Edge Detector 的架構圖，利用相鄰兩個 delay cell 的輸出 ( $V_{dl,j}$ 、 $V_{dl,j+1}$ ) 來對  $CK_{ref}$  取樣，再經過 XOR 閘便可得到在此 delay cell 區間內是否發生  $CK_{ref}$  轉態事件的訊號  $V_{ed,j}$ 。圖 3C.19 為此 Edge Detector 的實現電路，圖 3C.18 中的兩個取樣 D flip-flop 採用比較器來實現，而在  $CK_{ref}$  輸入端加上 chopper 則可降低比較器偏移電壓 (offset voltage) 對統計結果的影響，圖 3C.20 為比較器的電路圖。

Fig 3C.18: Edge Detector 架構圖。

Fig 3C.19: Edge Detector 電路圖。

Fig 3C.20: 比較器電路圖。

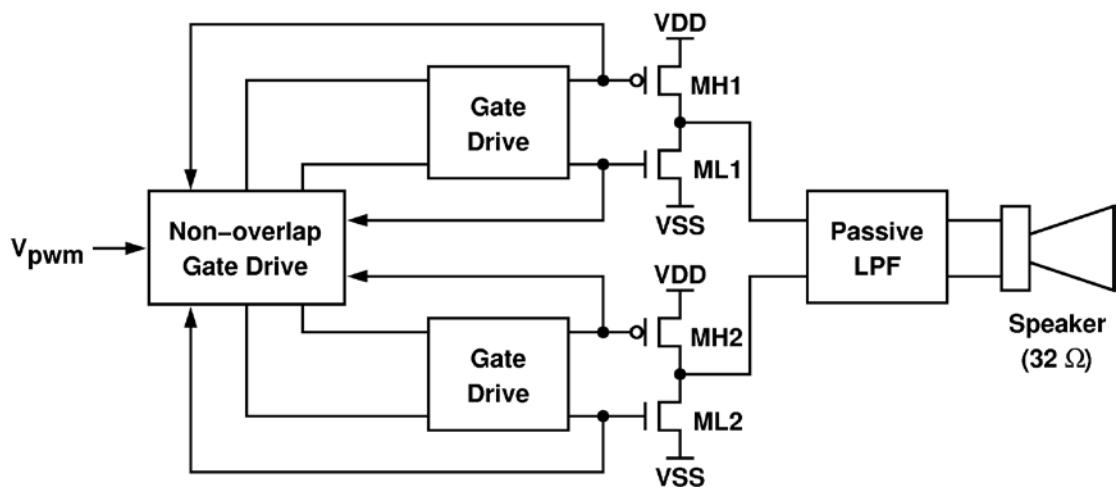

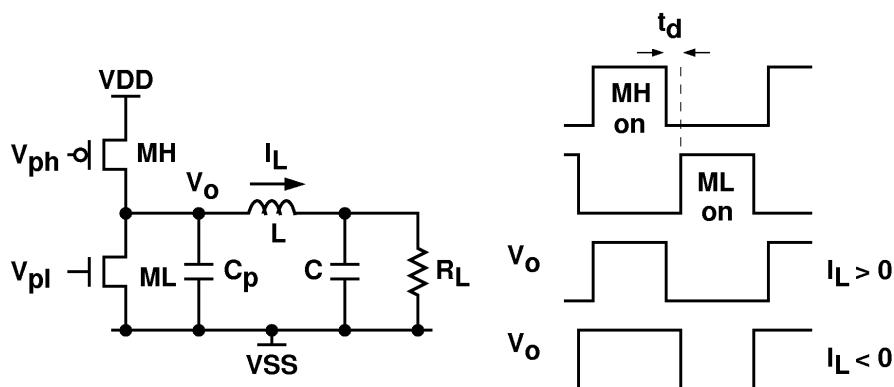

在 Class-D 放大器中，輸出級電路（Output Driver）對於整體放大器的失真表現和功率轉換效率有直接且顯著的影響。圖 3C.21 為 Class-D 輸出級電路之示意圖，此電路接收前述數位 PWM Class-D 調變電路的輸出  $V_{pwm}$ ，經由開關電晶體（switching transistors） $MH1,2$ 、 $ML1,2$  驅動低通濾波器和喇叭所組成的負載。由於功率轉換效率和訊號線性度的考量，開關電晶體必須具備非常低的導通電阻。為了避免開關電晶體  $MH1$ 、 $ML1$  ( $MH2$ 、 $ML2$ ) 同時導通，使用 Non-overlap Gate Drive 電路以引入一無效時間（dead time）。輸出級電路的種種非理想效應將造成音頻訊號線性度的失真，其錯誤來源為（1）開關電晶體的導通電阻；（2）dead time 失真；（3）脈衝訊號轉態（transition）延遲時間；（4）脈衝訊號的有限上升和下降時間（rise and fall times）。每項錯誤來源將分述在以下各段。

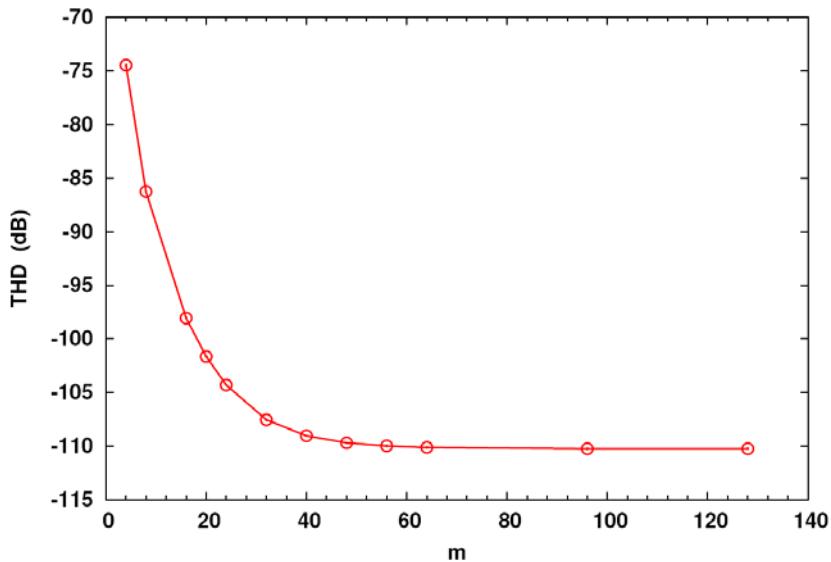

Fig 3C.21: Class-D 放大器輸出級電路。

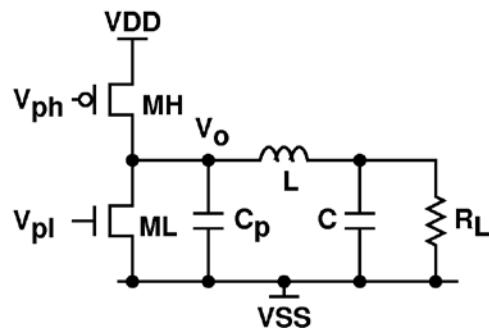

Fig 3C.22: 輸出級電晶體和 L-C 低通濾波器。

圖 3C.22 為單邊之輸出級電晶體和 L-C 低通濾波器示意圖，MH 和 ML 為輸出級開關電晶體， $R_L$  為喇叭的等效阻抗。輸出級開關電晶體作為開關使用並提供  $R_L$  和低通濾波器所需的負載電流。理想上，當電晶體 MH 導通時  $V_o$  的電壓會被拉到  $VDD$ ，反之當 ML 導通時  $V_o$  被拉到  $VSS$ 。電晶體的導通電阻上的跨壓將會使得  $V_o$  的電壓偏離  $VDD$  和  $VSS$ ，若導通電阻的阻值為一固定值，此導通電阻的效應將只會降低功率轉換效率。不幸地，電晶體的導通電阻會隨著流經電晶體的電流大小而改變，因此導通電阻的阻值大小會與輸入訊號相關，此一隨著輸入訊號改變的電阻將會造成音頻輸出訊號的失真。圖 3C.23 為開關電晶體導通電阻失真之頻譜圖，其中電晶體 MH 和 ML 的尺寸  $W/L$  分別為  $4 \times (520\mu / 0.12\mu)$  和  $4 \times (180\mu / 0.12\mu)$ ，由圖可看出開關電晶體導通電阻會導致顯著的諧波失真。開關電晶體尺寸大小與 THD 的關係如圖 3C.24 所示，其中電晶體 MH 和 ML 的尺寸  $W/L$  分別為  $m \times (520\mu / 0.12\mu)$  和  $m \times (180\mu / 0.12\mu)$ 。當  $m > 48$ ，導通電阻導致的諧波失真將低於 16 位元的量化雜訊位準，選取  $m \geq 20$ ，可達到 -100 dB 以上的 THD。

Fig 3C.23: 開關電晶體導通電阻失真頻譜圖。

Fig 3C.24: 開關電晶體尺寸與總諧波失真關係圖。

Fig 3C.25: Dead time 失真。

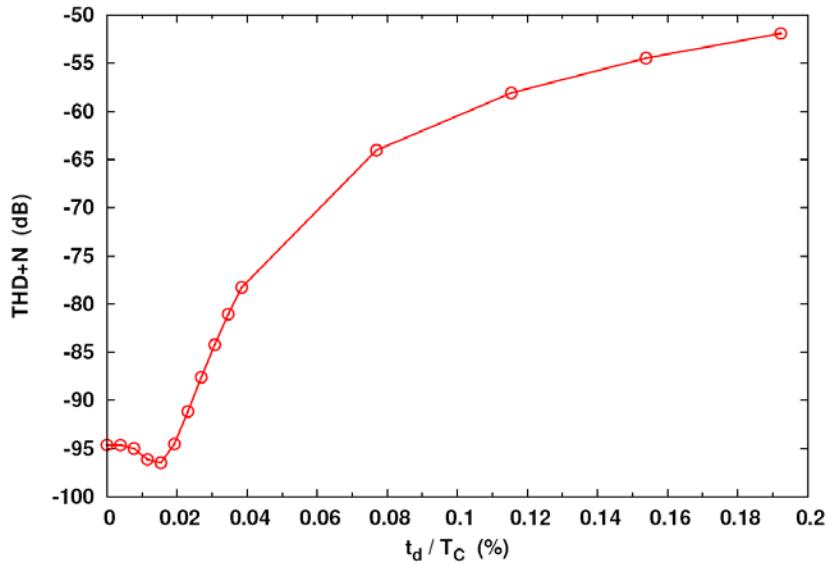

圖 3C.25 為 dead time 失真之示意圖， $I_L$  為流經電感 L 的電流。為了避免開關電晶體同時導通而形成一條流經 VDD 到 VSS 的低電阻路徑，在輸出級電路中

必須引入一段無效時間  $t_d$ ，在此區間內電晶體 MH 和 ML 皆不導通。加入 dead time 雖能防止貫通電流（shoot-through current）出現以提高功率轉換效率和避免電晶體損壞，但其輸出訊號  $V_o$  却會產生與輸入訊號有關的誤差（如圖 3C.25 所示），造成音頻訊號的失真。由 dead time 所造成的總諧波失真可表示為：

$$\text{THD} = \frac{\left( \frac{1}{2} - \frac{2\alpha_d}{\pi} \right)^2}{\sum_{k=3,5,\dots} \left( \frac{2\alpha_d}{\pi k} \right)^2}$$

其中  $\alpha_d = t_d / T_C$ ， $T_C$  為 PWM 脈衝訊號的週期。圖 3C.26 為一含有 dead time 失真之輸出訊號的頻譜圖 ( $t_d = 1 \text{ ns}$ ,  $T_C = 2.6 \text{ us}$ )，由圖可明顯看出加入 dead time 在輸出端會有奇數倍頻諧波的產生。圖 3C.27 是  $t_d$  和 THD+N 的關係圖，欲達到  $\text{THD}+\text{N} < -90 \text{ dB}$  的表現，無效時間和脈衝訊號週期的比值  $t_d/T_C$  必須低於 0.02%，以  $T_C = 2.6 \text{ us}$  為例， $t_d$  須小於 0.5 ns。

Fig 3C.26: 具 dead time 失真之頻譜圖 ( $t_d = 1 \text{ ns}$ ,  $T_c = 2.6 \text{ us}$ )。

Fig 3C.27: 無效時間  $t_d$  和與 THD+N 關係圖 ( $T_c = 2.6 \mu s$ )。

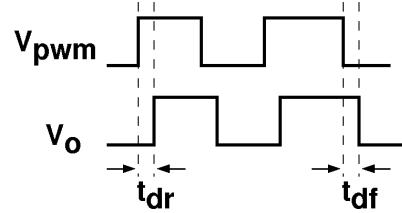

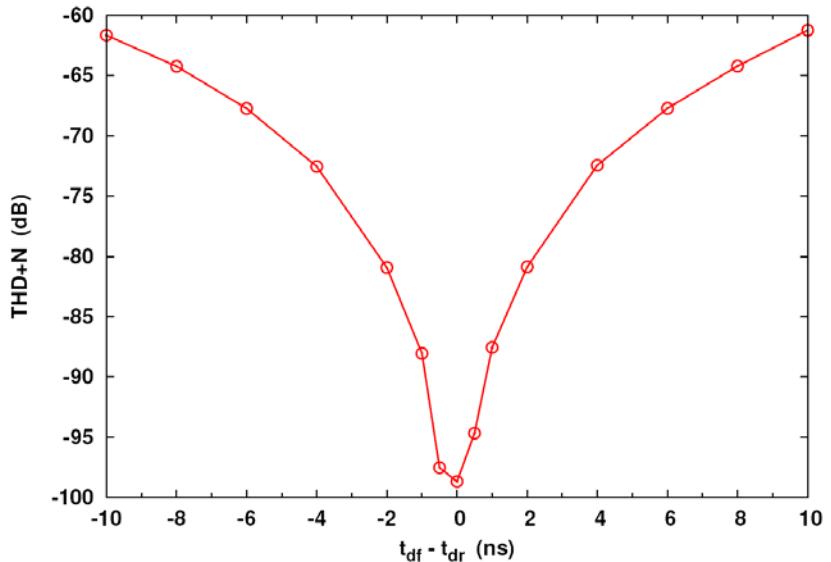

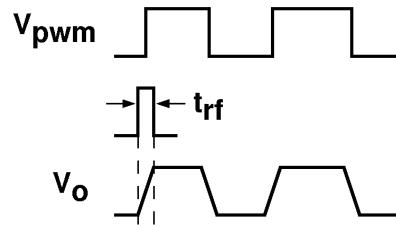

由於電晶體的有限導通 (turn-on) 與關閉 (turn-off) 時間，使得脈衝訊號在轉態時會有上升延遲時間  $t_{dr}$  和下降延遲時間  $t_{df}$  的產生 (如圖 3C.28 所示)。上升和下降延遲時間的差值  $t_{df} - t_{dr}$  會造成訊號線性度的失真，圖 3C.29 為  $t_{df} - t_{dr}$  與 THD+N 的關係圖。以現今的製程技術來看，延遲時間  $t_{dr}$  和  $t_{df}$  的絕對值通常為數個 ns 或更小，因此延遲時間在 Class-D 輸出級電路的設計中並非決定訊號線性度的主要參數。

Fig 3C.28: 脈衝訊號轉態延遲時間。

Fig 3C.29:  $t_{df} - t_{dr}$  與 THD+N 關係圖。

考量輸出脈衝有限上升與下降時間對音頻訊號的影響，由於上升與下降的轉態時間有所不同，且其轉態特性為非線性，為了簡化起見，假設其特性為線性上升與下降且上升與下降的時間均為  $t_{rf}$  (如圖 3C.30 所示)。經由這樣的假設，輸出訊號  $V_O$  可看成輸入訊號  $V_{pwm}$  與一寬度為  $t_{rf}$  的脈衝訊號作迴旋積(convolution)。因此，輸出訊號為：

$$V_O(f) = V_{pwm}(f) \cdot H_{rf}(f) \text{ where } H_{rf}(f) = \frac{\sin(\pi f t_{rf})}{\pi f t_{rf}}$$

以  $t_{rf} = 10 \text{ ns}$  為例， $H_{rf}$  之-3dB 頻率將高於 40 MHz。因此有限上升與下降時間對輸出訊號線性度的表現也非決定性的參數。

Fig 3C.30: 有限上升與下降時間。

根據以上的分析，表 3C.3 為設計一 THD+N 低於-90 dB 的 Class-D 輸出級電路之各項參數。

Table 3C.3: Class-D 輸出級電路設計參數。

|                               |          |

|-------------------------------|----------|

| Transistor size (m)           | > 20     |

| Dead time ( $t_d$ )           | < 0.5 ns |

| Delay ( $t_{dr}$ , $t_{df}$ ) | < 0.5 ns |

| Rise/Fall time ( $t_{rf}$ )   | < 1 ns   |

綜合以上所述，我們設計了一個適合於低功率助聽器系統的數位 Class D 喇叭驅動電路，表 3C.4 為其主要設計規格摘要。此驅動電路主要分為兩個區塊：數位 PWM Class-D 調變電路和輸出級電路。數位 PWM Class-D 調變電路包含了 APWM、3<sup>rd</sup>-order Noise Shaper 和混合型 Pulse Generator。我們提出了一個具延遲線時間歪斜校正之混合型 Pulse Generator，藉由此校正技術，延遲線延遲單元間的時間歪斜所造成的 SNR 下降可被補償，由 81 dB 提升至 94 dB。APWM、3<sup>rd</sup>-order Noise Shaper 和 Pulse Generator 中的 Timing Skew Estimator 為純數位電路，由數位合成實現，功率消耗約為 100 uW，其餘類比及混合訊號電路約為 140 uW。輸出級電路中影響系統表現的主要參數為開關電晶體導通電阻和 dead time，在符合系統 THD+N 的規格下選取電晶體大小及設計 dead time 以達到最佳的功率轉換效率。

Table 3C.4: 數位 Class-D 喇叭驅動電路規格。

| System Feature        |        |

|-----------------------|--------|

| Power Supply          | 1.2 V  |

| Signal Bandwidth      | 20 kHz |

| Output Load           | 32 Ω   |

| Digital PWM Modulator |        |

| THD@6.67 kHz Input    | -92 dB |

| SNR                   | 94 dB  |

| Digital Power         | 100 uW |

| Analog Power          | 140 uW |

| Output Driver         |        |

| THD+N                 | -90 dB |

| Maximum Output Power  | 18 mW  |

| Power Efficiency      | 91 %   |

## 參考文獻

- [Adrian09] V. Adrian, J. S. Chang, and B.-H. Gwee, “A Low-Voltage Micropower Digital Class-D Amplifier Modulator for Hearing Aids,” *IEEE Tran. Circuits Syst. I*, vol. 56, no. 2, pp. 337-349, Feb. 2009.

- [Kim06] S. Kim, N. Cho, S.-J. Song, D. Kim, K. Kim, and H.-J. Yoo, “A 0.9-V 96-μW Digital Hearing Aid Chip with Heterogeneous Σ-Δ DAC,” in *IEEE Symposium on VLSI Circuits* 2006, pp. 68-69, June 2006.

- [Pascual00] C. Pascual and B. Roeckner, “Computationally efficient conversion from pulse-code-modulation to naturally-sampled pulse-width-modulation,” in *Proc. 109<sup>th</sup> AES Convention*, Sept. 2000.

## 四、結論

本計畫是國科會「高階助聽器晶片及系統」的子計畫之一。本計畫是先前計畫的延續。本計畫的目的是持續改良並創新助聽器晶片所需的類比電路，包括(1) 類比數位轉換器；(2) 數位 Class-D 喇叭驅動電路；(3) 數位電源控制電路。

在麥克風接收端，我們用市面可購買到的原件設計並實現了一個麥克風可變增益放大器。此電路可以直接用於總計畫的助聽器 Prototype 系統中。而此經驗可幫助我們設計助聽器晶片中的麥克風放大器電路。

我們重新設計了一個音頻差積調變器 (Delta-Sigma Modulator, DSM)。此 DSM 已經用 TSMC 90 nm CMOS 製程製作成晶片，且量測成功。。此 DSM 有 24.4 kHz 的訊號頻寬， $\pm 800$  mV 的差動輸入範圍，100 dB 的動態範圍。在 1 V 的電壓下操作，只消耗 860  $\mu$ W 的功率。

我們持續在設計一個我們設計了一個數位式 Class-D 喇叭驅動電路。為了降低功率消耗，我們採用 Pulse-Width Modulation (PWM) 的調變方式。數位音頻訊號會先經過一個內插器 (Interpolator) 進行超取樣。接著內插過後的訊號經過 Digital PWM 轉換成代表脈衝寬度的訊號。在轉成實際脈衝訊號之前，數位脈衝寬度訊號會透過一個 Noise Shaper 轉為較少位元訊號，如此便能在不損失訊號精確度的前提下降低 Pulse Generator 的時脈頻率，降低電路的功率消耗。最後，我們採用混合計數器與延遲線的架構來實現 Pulse Generator。此架構可以降低計數器的操作頻率並減少延遲單元數目以簡化延遲線的設計。我們提出了一個延遲線時間歪斜 (Timing Skew) 校正技術，可以補償因延遲線延遲單元間的時間歪斜所造成的 SNR 下降的問題。此數位式 Class-D 喇叭驅動電路已經完成設計與佈局，目前正在製作成晶片中。

因為人手不足，目前暫停數位電源控制電路的設計。

出席國際會議報告

2013 年國際固態電路會議

2013 IEEE International Solid-State Circuits Conference

吳介琮 國立交通大學電子工程系所

## 1. 參加會議經過

國際固態電路會議(International Solid-State Circuits Conference, 簡稱 ISSCC) 每年二月中旬在美國加州的舊金山市舉行。ISSCC 是積體電路領域中，最大、最具頂尖望，也是最重要的年度會議。今年的會期是從 2 月 17 日至 2 月 21 日。大會宣稱註冊人數大約 3000 人。與會人員大都來自全球各大電子公司、研究機構、及學術單位。

會議的地點是在舊金山市市區的 Marriott Marquis Hotel。在會議期間我就住在附近的一家比較便宜的旅館。

會議 3 天分成 27 節(Sessions)，共發表 209 篇論文。論文之發表每天有早上 8:30-12:00，和下午 1:30-5:30 兩時段。每一時段有五個或六個平行的節同時進行。今年的論文有 36% 來自北美地區，40% 來自遠東地區，24% 來自歐洲地區。這是一個真正的國際性會議。用機構來分，論文有 55% 來自學術機構，37% 來自產業界，8% 來自獨立實驗室或研究單位。顯示本會議產學並重的特性。

ISSCC 主要在展現最新積體電路的研發成果，包括積體電路設計在性能上的突破，與積體電路的新式應用。論文種類有大型數位處理器、高性能晶片系統 (SOC)、記憶體、無線通訊、有線通訊、感測器、顯示器、微機電系統、生醫系統等。而在電路設計技術方面則有微波電路、射頻電路、PLL、類比電路、資料轉換電路、DC/DC 轉換電路、能源擷取電路、特殊數位電路等。

會議的第一天的上午，除了開幕典禮以及頒獎之外，還有 Plenary Session。其中包含 4 場邀請的演講，每場 35 分鐘。受邀請的演講者通常是分別來自美洲、歐洲、以及亞洲的電子業領導人物。今年的講員分別是來自美國的 AMD 公司、歐洲的 ASML 公司、日本的 Panasonic 公司，以及美國加州理工學院。

除此之外，會議期間從晚上 8:00 開始還有三場 Evening Discussion Session (EP)，以及三場 Evening Session (ES)。在 EP 中，Panelist 會和台下的參與者互動討論，而 ES 只是單純的幾位專家的演講。今年的 EP 的主題分別是：(1) Antiques from the Innovations Attic; (2) You're Hired – The Top 25 Interview Questions for Circuit Designers; (3) Empowering the Killer SoC Applications of 2020。ES 的主題分別是：(1) Student Research Review; (2) Batteries Not Included – How Little is Enough for Real Energy Autonomy? (3) High-speed Communications on 4 Wheels – What's in your Next Car?

本會除了 3 天之正規議程外，另外還有 2 天之活動，包括 10 個 Tutorial、6 個 Forum、及一個 Short Course。這些附屬研討會都是找專家來介紹現今熱門之積體電路及其設計技術。每一場都要另外收費。

## 2. 與會心得

今年的會議主題是”60 Years of (Em)Powering the Future”。今年是 ISSCC 的第 60 週年，因此大會安排的一些回顧活動，並勉勵大家繼續向前邁進。Plenary Session 中的講題通常與會議主題相連結。今年的講題有(1) Architecting the Future through Heterogeneous Computing; (2) Smart Life Solution from Home to City; (3) Continuing to Shrink: Next-Generation Lithography – Progress and Prospects; (4) The Evolution of Technology。演講 Heterogeneous Computing 是 AMD 公司的 VP。她基本上是在推銷公司的 CPU 與 GPU。她用 Star Trek 影集中的 Holodeck 虛擬環境做為例子，估計其所需要的運算量，而提出所謂的 CPU 配合 GPU 的 Heterogeneous Computing。其實這些都是已知的觀念，不是新東西。接下來是 Panasonic 公司的 CTO 演講的 Smart Life 觀念。其實就是將所有的消費性產品，包括家用的電器產品，配上智慧型處理器以及網路，如此可以將電器產品個人化並達省電的目的。第三位是 ASML 公司的 VP，主講用於積體電路製造中下一代的顯影技術。由於內容過於專業，我聽不太懂。最後一位則是赫赫有名的 CalTech 退休教授 Carver Mead。然而他卻在台上，沒有一張投影片，一個人喃喃自語 15 分鐘。我完全不知道他在講什麼，非常失望。

今年我進去聽論文的 Session 主要是與類比積體電路相關。Session 4 的主題是 Harvesting & Wireless Power。論文包括無線充電技術、太陽能電源轉換技術、壓電能源轉換技術等。技術重點都是要提升能源轉換的效能。Session 10 的主題是 Analog Techniques。論文包括各種不同應用的濾波器、放大器、以及振盪器等。比較有趣的電路技術包括 Multi-Phase Switched Capacitor Filter 以及 Multi-Path Amplifier。

Session 15 的主題是 Data Converter Techniques。論文有 MTK 的 Wide-Band Continuous-Time Delta-Sigma Modulator。此設計綜合了一些不同的技術而設計出目前最省電的 Wide-Band DSM。另外有幾篇 SAR ADC 的論文。SAR ADC 的優勢是省電，而這些論文用一些新的電路技術則可以提升解析度或速度。

Session 22 的主題是 Sensors & Displays。論文包括各種與感測器結合的感測電路。由於感測器的訊號都很小，這些電路要非常小心的處理雜訊以及干擾等問題。感測器包括 MEMS 加速感測器、麥克風、電流偵測器、觸控面板等。

Session 26 的主題是 High-Speed Data Converters。其中有用於 10G Ethernet 的 6-Bit 10GS/s Flash Time-Interleaved ADC，有用於寬頻無線接收器的 11-Bit 3.6GS/s SAR Time-Interleaved ADC，有用於高階示波器的 14-Bit 2.5GS/s Pipelined Time-Interleaved ADC。這些 Time-Interleaved 都需要校正，設計都很複雜。

## 3. 攜回資料名稱及內容

- 國際固態電路會議論文集與其 DVD ( 2013 IEEE International Solid-State Circuits Conference, Digest of Technical Papers )。

# 國科會補助計畫衍生研發成果推廣資料表

日期:2014/01/03

|           |                                                       |

|-----------|-------------------------------------------------------|

| 國科會補助計畫   | 計畫名稱: 總計畫暨子計畫五：助聽器類比積體電路設計(3/3)                       |

|           | 計畫主持人: 吳介琮                                            |

|           | 計畫編號: 101-2220-E-009-014- 學門領域: 晶片科技計畫--整合型學術研究<br>計畫 |

| 無研發成果推廣資料 |                                                       |

# 101 年度專題研究計畫研究成果彙整表

|                                            |                 |                          |                 |            |      |                                     |

|--------------------------------------------|-----------------|--------------------------|-----------------|------------|------|-------------------------------------|

| 計畫主持人：吳介琮                                  |                 | 計畫編號：101-2220-E-009-014- |                 |            |      |                                     |

| 計畫名稱：高階助聽器晶片及系統--總計畫暨子計畫五：助聽器類比積體電路設計(3/3) |                 |                          |                 |            |      |                                     |

| 成果項目                                       |                 | 量化                       |                 |            | 單位   | 備註（質化說明：如數個計畫共同成果、成果列為該期刊之封面故事...等） |

|                                            |                 | 實際已達成數（被接受或已發表）          | 預期總達成數(含實際已達成數) | 本計畫實際貢獻百分比 |      |                                     |

| 國內                                         | 論文著作            | 期刊論文                     | 0               | 0          | 100% | 篇                                   |

|                                            |                 | 研究報告/技術報告                | 0               | 0          | 100% |                                     |

|                                            |                 | 研討會論文                    | 0               | 0          | 100% |                                     |

|                                            |                 | 專書                       | 0               | 0          | 100% |                                     |

|                                            | 專利              | 申請中件數                    | 0               | 0          | 100% | 件                                   |

|                                            |                 | 已獲得件數                    | 0               | 0          | 100% |                                     |

|                                            | 技術移轉            | 件數                       | 1               | 0          | 100% | 件                                   |

|                                            |                 | 權利金                      | 0               | 0          | 100% | 千元                                  |

|                                            | 參與計畫人力<br>(本國籍) | 碩士生                      | 20              | 0          | 100% | 人次                                  |

|                                            |                 | 博士生                      | 13              | 0          | 100% |                                     |

|                                            |                 | 博士後研究員                   | 0               | 0          | 100% |                                     |

|                                            |                 | 專任助理                     | 0               | 0          | 100% |                                     |

| 國外                                         | 論文著作            | 期刊論文                     | 3               | 0          | 100% | 篇                                   |

|                                            |                 | 研究報告/技術報告                | 0               | 0          | 100% |                                     |

|                                            |                 | 研討會論文                    | 11              | 0          | 100% |                                     |

|                                            |                 | 專書                       | 0               | 0          | 100% | 章/本                                 |

|                                            | 專利              | 申請中件數                    | 1               | 0          | 100% | 件                                   |

|                                            |                 | 已獲得件數                    | 0               | 0          | 100% |                                     |

|                                            | 技術移轉            | 件數                       | 0               | 0          | 100% | 件                                   |

|                                            |                 | 權利金                      | 0               | 0          | 100% | 千元                                  |

|                                            | 參與計畫人力<br>(外國籍) | 碩士生                      | 0               | 0          | 100% | 人次                                  |

|                                            |                 | 博士生                      | 0               | 0          | 100% |                                     |

|                                            |                 | 博士後研究員                   | 0               | 0          | 100% |                                     |

|                                            |                 | 專任助理                     | 0               | 0          | 100% |                                     |

|                                                                                                          |                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p><b>其他成果</b><br/>           (無法以量化表達之成果如辦理學術活動、獲得獎項、重要國際合作、研究成果國際影響力及其他協助產業技術發展之具體效益事項等，請以文字敘述填列。)</p> | <p>本助聽器計畫涵蓋多項不同領域之專長，技術成果包括人類聽覺模型、針對華語之助聽補償策略、語音訊號處理技術、雙耳通訊技術、助聽器系統發展平台、超低功率微處理器與數位訊號處理器、超低功率系統晶片設計技術、超低功率類比電路設計技術、微機電式聲學元件、微機電異質整合封裝技術等。以上這些技術除了發展醫療用的助聽器之外，還可以應用於特殊聽覺感應系統、多媒體之高性能耳機、以及各種超低功率之晶片系統等。</p> |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 科<br>教<br>處<br>計<br>畫<br>加<br>填<br>項<br>目 | 成果項目            | 量化 | 名稱或內容性質簡述 |

|-------------------------------------------|-----------------|----|-----------|

|                                           | 測驗工具(含質性與量性)    | 0  |           |

|                                           | 課程/模組           | 0  |           |

|                                           | 電腦及網路系統或工具      | 0  |           |

|                                           | 教材              | 0  |           |

|                                           | 舉辦之活動/競賽        | 0  |           |

|                                           | 研討會/工作坊         | 0  |           |

|                                           | 電子報、網站          | 0  |           |

|                                           | 計畫成果推廣之參與（閱聽）人數 | 0  |           |

# 國科會補助專題研究計畫成果報告自評表

請就研究內容與原計畫相符程度、達成預期目標情況、研究成果之學術或應用價值（簡要敘述成果所代表之意義、價值、影響或進一步發展之可能性）、是否適合在學術期刊發表或申請專利、主要發現或其他有關價值等，作一綜合評估。

## 1. 請就研究內容與原計畫相符程度、達成預期目標情況作一綜合評估

- 達成目標

未達成目標（請說明，以 100 字為限）

實驗失敗

因故實驗中斷

其他原因

說明：

由於新竹馬偕醫院無法找到合適且志願的聽障者，本計畫原先規畫的人體實驗因而延宕，導致目前無法完整的驗證本計畫所開發的硬體及新式聽力補償策略。然而本計畫另外有開發其他不需要人體實驗的技術，如噪音消除。此技術已經技轉予廠商。我們已經將部分的人體實驗轉與花蓮慈濟醫院合作。

由於本團隊資源有限，助聽器原形系統整合工作無法順利進行。我們有試圖尋找產業界的合作，希望以產學計畫方式，共同開發，整合晶片及系統。台灣本地的助聽器製造商的規模都不大，沒有財力投資 IC 設計。而由於助聽器晶片的市場目前很小，台灣的 IC 設計公司都不願意投入。本團隊曾接觸多家廠商，如明展生醫、元勛國際、美樂迪、瑞昱半導體、鑫創等，商討技術轉移的可能性。但是都沒有形成實際合作計畫。

## 2. 研究成果在學術期刊發表或申請專利等情形：

論文：已發表 未發表之文稿 撰寫中 無

專利：已獲得 申請中 無

技轉：已技轉 洽談中 無

其他：(以 100 字為限)

本計畫於 102 年發表國外期刊論文 3 篇，國外研討會論文 11 篇，專利申請 1 件，產學合作 1 件。

本計畫開發的衍生性技術，如雜音消除，有技轉給 IC 設計公司。

## 3. 請依學術成就、技術創新、社會影響等方面，評估研究成果之學術或應用價值（簡要敘述成果所代表之意義、價值、影響或進一步發展之可能性）(以 500 字為限)

本助聽器計畫涵蓋多項不同領域之專長，技術成果包括人類聽覺模型、針對華語之助聽補償策略、語音訊號處理技術、雙耳通訊技術、助聽器系統發展平台、超低功率微處理器與數位訊號處理器、超低功率系統晶片設計技術、超低功率類比電路設計技術、微機電式聲學元件、微機電異質整合封裝技術等。以上這些技術除了發展醫療用的助聽器之外，還可以應用於特殊聽覺感應系統、多媒體之高性能耳機、以及各種超低功率之晶片系統等。