# Impacts of Fluorine Ion Implantation With Low-Temperature Solid-Phase Crystallized Activation on High- $\kappa$ LTPS-TFT

Ming-Wen Ma, Student Member, IEEE, Chih-Yang Chen, Student Member, IEEE, Chun-Jung Su, Student Member, IEEE, Woei-Cherng Wu, Student Member, IEEE, Yi-Hong Wu, Tsung-Yu Yang, Kuo-Hsing Kao, Tien-Sheng Chao, Senior Member, IEEE, and Tan-Fu Lei, Member, IEEE

Abstract—In this letter, fluorine ion implantation with low-temperature solid-phase crystallized activation scheme is used to obtain a high-performance HfO2 low-temperature poly-Si thin-film transistor (LTPS-TFT) for the first time. The secondary ion mass spectrometer (SIMS) analysis shows a different fluorine profile compared to that annealed at high temperature. About one order current reduction of  $I_{\rm min}$  is achieved because 25% grain-boundary traps are passivated by fluorine implantation. In addition, the threshold voltage instability of hot carrier stress is also improved with the introduction of fluorine. The LTPS-TFT with HfO2 gate dielectric and fluorine preimplantation can simultaneously achieve low  $V_{\rm TH} \sim 1.32$  V, excellent subthreshold swing  $\sim$ 0.141 V/dec, and high  $I_{\rm ON}/I_{\rm min}$  current ratio  $\sim$ 1.98  $\times$  107.

Index Terms—Fluorine implantation, high- $\kappa$ , hot carrier stress, low-temperature poly-Si thin-film transistors (LTPS-TFTs).

# I. INTRODUCTION

IGH-PERFORMANCE low-temperature poly-Si thin-film transistors (LTPS-TFTs) are recently developed for the employment of active-matrix liquid crystal displays on a glass substrate and for driving integrated circuits for the application of system-on-panel (SOP) [1]–[3]. However, there are many defects at the grain boundary of poly-Si channel film, resulting in the degradation of LTPS-TFTs' performance [4]. In order to make the channel more conductive, grain traps of the poly-Si channel film must be passivated. Therefore, a large operation voltage was needed for the conventional LTPS-TFTs without any defects passivation [5]–[9]. The grain defects of the poly-Si channel film would result in poor subthreshold swing (S. S.), high minimum drain–current ( $I_{\min}$ ), and large threshold voltage ( $V_{\mathrm{TH}}$ ).

Manuscript received October 5, 2007; revised November 15, 2007. This work was supported by the National Science Council, Taiwan, under Contract NSC-95-2221-E-009-272. The review of this letter was arranged by Editor J. Sin.

M.-W. Ma, C.-Y. Chen, C.-J. Su, and T.-F. Lei are with the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: william.ee94g@nctu.edu.tw; cyc.ee92g@nctu.edu.tw; cjsu.ee91g@nctu.edu.tw; tflei@faculty.nctu.edu.tw;)

W.-C. Wu, T.-Y. Yang, K.-H. Kao, and T.-S. Chao are with the Institute and Department of Electrophysics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: m9128104@stmail.cgu.edu.tw; owen0901.ep94g@nctu.edu.edu.tw; frank711110@yahoo.com.tw; tschao@mail.nctu.edu.tw).

Y.-H. Wu is with the Department of Electronic Engineering, Feng Chia University, Taichung 40724, Taiwan, R.O.C. (e-mail: honghong5023@gmail.com). Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2007.914071

The adopting of high- $\kappa$  gate dielectric is one of the effective ways to improve the performance of LTPS-TFTs [10]-[12]. A larger gate capacitance with the same physical thickness by using high- $\kappa$  gate dielectric instead of  $SiO_2$  gate oxide can attract more carriers with a smaller voltage to turn on the LTPS-TFTs. In spite of the employment of high- $\kappa$  gate dielectrics, the defects of the poly-Si channel film still exist that contribute to high drain leakage current [4]. Therefore, defects passivation is necessary to improve the drain leakage current and  $I_{\rm ON}/I_{\rm min}$  current ratio. Hydrogen plasma treatment is the most popular approach used to passivate defects and reduce the leakage current [13]–[15]. However, the introduction of hydrogen would degrade the reliability due to the weak Si-H bonds [16], [17]. To solve this problem, fluorine implantation is a promising alternative to create strong Si-F bonds [5]-[9]. Subsequent high-temperature processes (≥700 °C) after fluorine implantation have been used for the deposition of tetraethylorthosilicate (TEOS) gate dielectric layer and passivation layer at 700 °C over 3 h [6], [7] and the growth of thermal oxide and dopant activation at 850 °C [8], [9], which causes fluorine ions to diffuse to the interfaces of gateoxide/poly-Si and poly-Si/buried-oxide and pile up in the interfaces. However, fluorine implantation with a low-temperature solid-phase crystallized activation (≦600 °C) has not been reported yet. In this letter, we found that the distribution of fluorine ions is totally different at high temperatures, the electrical performance can be improved significantly.

# II. EXPERIMENTAL PROCEDURE

The fabrication of devices started by depositing a 50 nm undoped amorphous Si ( $\alpha$ -Si) layer at 550 °C in a low-pressure chemical vapor deposition system on Si wafers capped with a 500-nm-thick thermal oxide layer. Then, the fluorine atoms were implanted at energy of 11 keV to a dosage of  $5 \times 10^{14}$  cm<sup>-2</sup>. The  $\alpha$ -Si layer was recrystallized by solid-phase crystallization (SPC) process in furnace at 600 °C for 24 h in a N<sub>2</sub> ambient. A 500-nm-thick plasma-enhanced chemical vapor deposition oxide was deposited at 300 °C for the device isolation. The oxide was then patterned and etched to define the active region of device. The source and drain regions in the active device region was implanted with phosphorus (15 keV at  $5 \times 10^{15}$  cm<sup>-2</sup>) and activated at 600 °C for 24 h annealing in a N<sub>2</sub> ambient. Then, a 75 nm HfO<sub>2</sub> was deposited by electron-beam evaporation system. An O<sub>2</sub> treatment in furnace was applied to improve the gate oxide quality at 400 °C for 30 min. After the patterning of

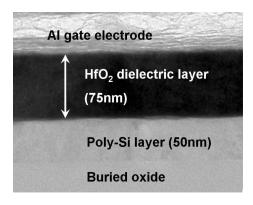

Fig. 1. Cross-sectional transmission electron microscopy (TEM) micrograph of the  $HfO_2$  gate dielectric TFT structure.

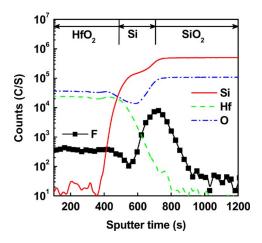

Fig. 2. SIMS analysis of the  $HfO_2$  LTPS-TFT with fluorine preimplantation.

contact holes, aluminum was deposited by thermal evaporation system and patterned as the probe pads to complete the TFT devices. There are no high-temperature processes (≥600 °C) during device fabrication.

Fig. 1 shows the cross-sectional transmission electron microscopy (TEM) micrograph of HfO $_2$  gate dielectric TFT structure. The measured device has gate length and width of 10 and 100  $\mu$ m, respectively. The  $V_{\rm TH}$  is defined as the gate voltage at which the drain–current reaches 100 nA  $\times$  W/L under  $V_D=0.1$  V. The field effect mobility  $\mu_{\rm FE}$  is extracted from the maximum transconductance ( $G_m$ ).

# III. RESULTS AND DISCUSSION

Fig. 2 shows the secondary ion mass spectrometer (SIMS) spectrum of  $HfO_2$  LTPS-TFT with fluorine implantation. We can observe that fluorine ions after postimplanted low-temperature SPC activation are merely piling up at the poly-Si/buried-oxide interface, and are not observed in the  $HfO_2$ /poly-Si interface. This distribution of fluorine ions is different from the results of high-temperature annealing that fluorine ions would pile up at the interfaces of both gate-oxide/poly-Si and poly-Si/buried-oxide [6]–[9]. This implies that the SPC activation of  $\alpha$ -Si with fluorine preimplantation would not affect the upper part of the channel film. The impacts of fluorine preimplantation with low-temperature SPC activation on the performance of  $HfO_2$  LTPS-

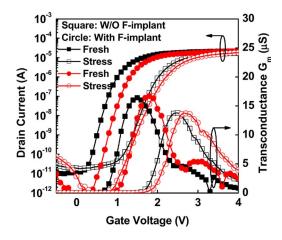

Fig. 3. Transfer characteristics  $(I_D - V_G \text{ and } G_m)$  of the HfO<sub>2</sub> LTPS-TFT at  $V_D = 0.1$  V without and with fluorine preimplantation before and after hot carrier stress for 1000 s.

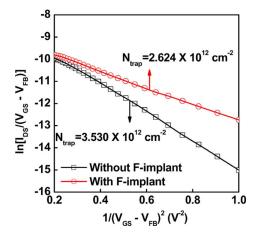

Fig. 4. Plots of ln  $[I_{\rm DS}/(V_{\rm GS}-V_{\rm FB})]$  versus  $1/(V_{\rm GS}-V_{\rm FB})^2$  curves at  $V_{\rm DS}=1$  V and high  $V_{\rm GS}$ .

TFTs are shown in Fig. 3. High-performance characteristics of HfO<sub>2</sub> LTPS-TFT with low  $V_{\rm TH}\sim 1$  V, excellent S. S.  $\sim 0.147$ V/dec, high mobility  $\sim$ 74.5 cm<sup>2</sup>/V·s, and high  $I_{\rm ON}/I_{\rm min}$  current ratio  $\sim 2.19 \times 10^6$  are observed without any treatment. After fluorine implantation, we can observe that the  $I_{\min}$  is reduced significantly from 9.78 to 1.09 pA at  $V_D = 0.1$  V. The  $I_{\min}$  can be attributed to the junction leakage current that is dominated by the grain-boundary trap-state densities  $(N_{\text{trap}})$  of poly-Si channel film [4]. The effective grain-boundary trap-state densities  $(N_{\rm trap})$  with and without fluorine implantation are also estimated by Levinson and Proano method [18], [19]. Fig. 4 exhibits the plots of  $\ln [I_{\rm DS}/(V_{\rm GS}-V_{\rm FB})]$  versus  $1/(V_{\rm GS}-V_{\rm FB})^2$ curves at  $V_{\rm DS}=1$  and high  $V_{\rm GS}$ , where the flat-band voltage  $(V_{\rm FB})$  is defined as the gate voltage that yields the minimum drain-current from the transfer characteristic. From Fig. 4, it is apparent that the effective grain-boundary trap-state densities decrease from  $3.530 \times 10^{12}$  to  $2.624 \times 10^{12}$  cm<sup>-2</sup> after fluorine passivation. This indicates that about 25.6% reduction in the effective grain-boundary trap-state densities is achieved due to the passivation of the grain-boundary trap-state densities in the lower part of the channel film. The important parameters of

|                   | V <sub>TH</sub> (V) | S.S.<br>(V/dec.) | μ <sub>EF</sub><br>(cm <sup>2</sup> /V-s) | I <sub>min</sub> (pA) | Ι <sub>on</sub><br>(μΑ) | $\frac{I_{on}/I_{min}}{(10^6)}$ | N <sub>trap</sub> (10 <sup>12</sup> cm <sup>-2</sup> ) | ΔV <sub>TH</sub> (V) |

|-------------------|---------------------|------------------|-------------------------------------------|-----------------------|-------------------------|---------------------------------|--------------------------------------------------------|----------------------|

| w/o<br>F-implant  | 1.01                | 0.147            |                                           |                       |                         | 2.19                            |                                                        |                      |

| with<br>F-implant | 1.32                | 0.141            | 75.9                                      | 1.09                  | 21.6                    | 19.82                           | 2.624                                                  | 0.89                 |

LTPS-TFTs are listed in the Table I. A slight increase of  $V_{\rm TH}$  from 1.01 to 1.32 V is observed after fluorine implantation. This is because lots of fluorine ions are incorporated in the buried oxide to form the negative fixed oxide charges to affect the channel film [20]. This subgate effect would make the channel less conductive, thus increasing the  $V_{\rm TH}$  [8]. However, the behaviors of significant  $I_{\rm min}$  reduction and a slight  $V_{\rm TH}$  increase of the fluorinated n-channel TFTs cannot be found in previous reports [6]–[9].

In addition to the performance enhancement of HfO $_2$  LTPS-TFT, the reliability of the devices under hot carrier stress with  $V_D=2(V_G-V_{\rm TH})=10$  V for 1000 s is also studied, as shown in Fig. 3. The behavior of about one order reduction of  $I_{\rm min}$  in the fluorinated TFT is still maintained, and shows a better threshold voltage instability  $\Delta V_{\rm TH}$  from 1.02 to 0.89 V. It also demonstrates that the treatment method of fluorine preimplantation with low-temperature SPC activation would improve the reliability of LTPS-TFTs, as shown in the previous reports [6]–[9]. Hydrogen treatment can also reduce the  $I_{\rm min}$  effectively. However, the introduction of hydrogen would seriously degrade the reliability of LTPS-TFTs and easily release during mediate temperature process ( $\geq$ 500 °C) [16], [17].

# IV. CONCLUSION

High-performance LTPS-TFT with  $HfO_2$  gate dielectric and fluorine preimplantation has been demonstrated. Low-temperature SPC activation of fluorine ions is reported for the first time, and it also provides an improved electrical characteristics and reliability. Thus, it would be useful for the application of SOP.

### ACKNOWLEDGMENT

The authors would like to thank the processes support from the National Nano Device Laboratory and the Nano Facility Center of the National Chiao Tung University.

### REFERENCES

K. M. Chang, W. C. Yang, and C. P. Tsai, "Electrical characteristics of low temperature polysilicon TFT with a novel TEOS/oxynitride stack gate dielectric," *IEEE Electron Device Lett.*, vol. 24, no. 8, pp. 512–514, Aug. 2003.

- [2] C. W. Lin, M. Z. Yang, C. C. Yeh, L. J. Cheng, T. Y. Huang, H. C. Cheng, H. C. Lin, T. S. Chao, and C. Y. Chang, "Effects of plasma treatments, substrate types, and crystallization methods on performance and reliability of low temperature polysilicon TFTs," in *IEDM Tech. Dig.*, 1999, pp. 305– 308.

- [3] W. G. Hawkins, "Polycrystalline-silicon device technology for large-area electronics," *IEEE Trans. Electron Devices*, vol. 33, no. 4, pp. 477–481, Apr. 1986.

- [4] K. R. Olasupo and M. K. Hatalis, "Leakage current mechanism in submicron polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 43, no. 8, pp. 1218–1223, Aug. 1996.

- [5] S.-D. Wang, W.-H. Lo, and T.-F. Lei, "CF4 plasma treatment for fabricating high-performance and reliable solid-phase-crystallized poly-Si TFTs," J. Electrochem. Soc., vol. 152, no. 9, pp. 703–706, 2005.

- [6] C.-H. Tu, T.-C. Chang, P.-T. Liu, C.-H. Chen, C.-Y. Yang, Y.-C. Wu, H.-C. Liu, L.-T. Chang, C.-C Tsai, S. M. Sze, and C.-Y. Chang, "Electrical enhancement of solid phase crystallized poly-Si thin-film transistors with fluorine ion implantation," *J. Electrochem. Soc.*, vol. 153, no. 9, pp. 815–818, 2006.

- [7] C.-H. Tu, T.-C. Chang, P.-T. Liu, H.-W. Zan, Y.-H. Tai, C.-Y. Yang, Y.-C. Wu, H.-C. Liu, W.-R. Chen, and C.-Y. Chang, "Enhanced performance of poly-Si thin film transistors using fluorine ions implantation," *Electrochem. Solid State Lett.*, vol. 8, no. 9, pp. 246–248, 2005.

- [8] C.-K. Yang, T.-F. Lei, and C.-L. Lee, "Characteristics of top-gate polysilicon thin-film transistors fabricated on fluorine-implanted and crystallized amorphous silicon films," *J. Electrochem. Soc.*, vol. 143, no. 10, pp. 3302– 3307, 1996.

- [9] H. N. Chern, C. L. Lee, and T. F. Lei, "The effects of fluorine passivation on polysilicon thin-film transistor," *IEEE Trans. Electron Devices*, vol. 41, no. 5, pp. 698–702, May 1994.

- [10] C.-P. Lin, B.-Y. Tsui, M.-J. Yang, R.-H. Huang, and C. H. Chien, "High-performance poly-silicon TFTs using HfO<sub>2</sub> gate dielectric," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 360–363, May 2006.

- [11] B. F. Hung, K. C. Chiang, C. C. Huang, A. Chin, and S. P. McAlister, "High-performance poly-silicon TFTs incorporating LaAlO<sub>3</sub> as the gate dielectric," *IEEE Electron Device Lett.*, vol. 26, no. 6, pp. 384–386, Jun. 2005

- [12] Z. Jin, H. S. Kwok, and M. Wong, "High-performance polycrystalline SiGe thin-film transistors using Al<sub>2</sub>O<sub>2</sub> gate insulators," *IEEE Electron Device Lett.*, vol. 19, no. 12, pp. 502–504, Dec. 1998.

- [13] T. Kamins and P. J. Marcoux, "Hydrogenation of transistors fabricated in polycrystalline silicon films," *IEEE Electron Device Lett.*, vol. 1, no. 8, pp. 159–161, Aug. 1980.

- [14] A. Mimura, N. Konishi, K. Ono, J.-I. Ohwada, Y. Hosokawa, Y. A. Ono, Y. Suzuki, K. Miyata, and H. Kawakami, "High performance low-temperature poly-Si n-channel TFT's for LCD," *IEEE Trans. Electron Devices*, vol. 36, no. 2, pp. 351–359, Feb. 1989.

- [15] I.-W. Wu, T.-Y. Huang, W. B. Jackson, A. G. Lewis, and A. C. Chiang, "Passivation kinetics of two types of defects in polysilicon TFI by plasma hydrogenation," *IEEE Electron Device Lett.*, vol. 12, no. 4, pp. 181–183, Apr. 1991.

- [16] S. Banerjee, R. Sundaresan, H. Shichijo, and S. Malhi, "Hot-camer degradation of n-channel polysilicon MOSFET's," *IEEE Trans. Electron De*vices, vol. 35, no. 2, pp. 152–157, Feb. 1988.

- [17] M. Hack, A. G. Lewis, and I.-W. Wu, "Physical models for degradation effects in polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 40, no. 5, pp. 890–897, May 1993.

- [18] J. Levinson, F. R. Shepherd, P. J. Scanlon, W. D. Westwood, G. Este, and M. Rider, "Conductivity behavior in polycrystalline semiconductor thin film transistors," *J. Appl. Phys.*, vol. 53, no. 2, pp. 1193–1202, Feb. 1982.

- [19] R. E. Proano, R. S. Misage, and D. G. Ast, "Development and electrical properties of undoped polycrystalline silicon thin-film transistor," *IEEE Trans. Electron Devices*, vol. 36, no. 9, pp. 1915–1922, Sep. 1989.

- [20] P. J. Wright and K. C. Saraswat, "The effect of fluorine in silicon dioxide gate dielectrics," *IEEE Trans. Electron Devices*, vol. 36, no. 5, pp. 879– 889, Sep. 1989.