## 行政院國家科學委員會專題研究計畫成果報告

# 無線寬頻分碼多工用戶接收機低功率晶片設計

### Low Power VLSI Chip Design for WCDMA Receiver

計畫編號: NSC-90-2213-E-009-069

執行期間: 90年8月1日至91年7月31日

計畫主持人:吳文榕教授 國立交通大學電信系

#### 一、中文摘要

本計畫本年度研究重點集中在研發 3GPP UTRA-FDD(WCDMA)下鏈路用戶接 收器低功率晶片設計。下鏈路用戶接收器 有雨大關鍵技術:(i)基地台細胞搜尋機 制(cell search)及(ii)相位鎖相迴路技 術 (phase locked loop)。目前細胞搜尋相 關低功率晶片設計方面論文相當有限。因 此本計畫提出整合 Biased number 表示法 平行處理 (parallel processing) 及排線式 (pipeline)低功率架構以期達到極佳的效 能。Biased-number表示法經由實際模擬 驗證其 transition activity 遠比其他表示法 為低,如此將使得基於 Biased-number 表 示法之運算硬體損耗功率較低。至於相位 鎖相迴路部份,本計畫提出擁有低面積改 良式冗餘算術座標旋轉演算法所設計之 直接數位頻率合成器設計之數位相位鎖 相迴路,本計畫係採用以 Xilinx Virtex/II 晶片 為實體測試平台進行硬軟體整合共同設計流程 (Hardware/Software Codesign)以期達到最佳效

關鍵詞:細胞搜尋機制、相位鎖相迴路、低功率晶片設計

#### 英文摘要

This project concerns low power VLSI chip design of 3GPP WCDMA (IMT-DS) mobile receiver and especially with emphasis on two key technologies:(1) cell search and (2) digital phase-locked loop (DPLL). This project is aimed at developing a low power VLSI chip design for the correlator involved in cell search using biased-number (BN) representation, pipelining and parallel technology. It could be shown that the BN-based chip is able to achieve the lowest power consumption than the other arithmetic representation. On the other hand, the low power design for DPLL includes low area CORDIC-based direct digital frequency synthesizer Finally, a Virtex/II-chip-based

hardware/software codesign testbed is implemented to verify the effectiveness of the low power design.

Keywords: WCDMA , cell search, DPLL, low power VLSI chip design

#### 二、 計畫緣由及目的

根據國際電信聯盟 < ITU > 的統計資料顯 示,到西元2000年底,行動電話將超過5億個用 户,約為固網9.5億個用戶的一半,根據估計,行 動電話到 2005 年將成為通訊的主流,超過固網。 第三代無線行動通訊系統強調多媒體服務的功 能,其傳輸速率為 384Kbps~2Mbps,主要領導系統 技術,包括日本的 W-CDMA、歐洲的 UTRA (W-CDMA 與 TD-CDMA 並存) 及美國的 cdma2000。但由於這三大系統標準並不盡相同,因 此 3GPP( 3rd generation Partnership Project )與 3GPP2 (3<sup>rd</sup> generation Partnership Project 2)之組織於焉產 生,用以協調各家之標準。其中3GPP聯盟為歐洲 Ericsson, Nokia 所主導,而 3GPP2 聯盟為北美所 主導。因為 CDMA (Code Division Multiple Access) 分碼多工進接系統在寬頻的使用效率上較好,所以 它成為第三代無線行動通訊系統 IMT-2000 無線傳 輸技術(RTT)的相關建議方案中(約有10個)最受 重視之技術。本計畫本年度研究重點將集中研發 3GPP UTRA-FDD(WCDMA)下鏈路用戶接收器低 功率晶片設計。下鏈路用戶接收器有兩大關鍵技 術:(i)基地台細胞搜尋機制(cell search)及(ii) 相位鎖相迴路技術 (phase locked loop)。3GPP WCDMA 系採用基地台細胞之間非同步系統 (inter-cell asynchronous system), 其中每一個基地 台細胞均擁有其獨特不同的攪拌碼(scrambling code)。目前攪拌碼總數為512並且分成64個群組, 其中每一個群組涵括有8個攪拌碼。因此若能先判 定涵蓋所需求攪拌碼的群組,再進一步自該群組 (code group) 中選定此一主攪拌碼,將可以有效 地提高細胞搜尋速度。3GPP WCDMA 細胞搜尋機 制[2]-[11]主要包括有(1)時格同步機制 (slot synchronization),(2)攪拌碼群組判定及資料框同步 機制 (Code group identification & frame synchronization) 及攪拌碼判定機制 (scrambling code identification)。目前細胞搜尋相關低功率晶片

設計方面論文相當有限即參考文獻[13]及[15]。因此本計畫提出低功率 biased-number 相關器架構以期達到極佳的效能。至於相位鎖相迴路部份,本計畫提出擁有低面積改良式冗餘算術(RB)座標旋轉演算法所設計之直接數位頻率合成器設計之數位相位鎖相迴路。

#### 三、 研究方法與成果

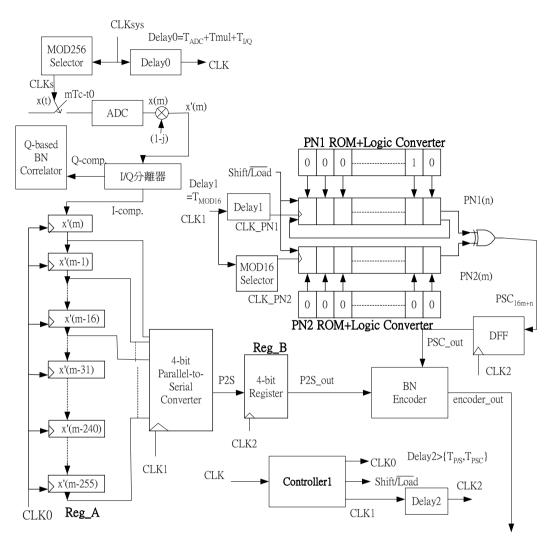

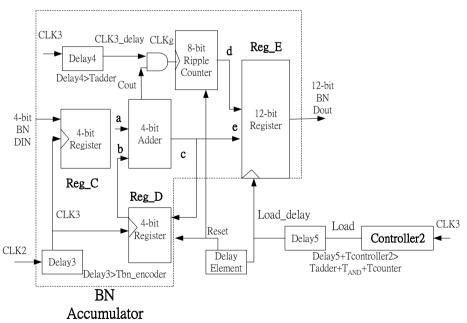

本研究計畫進行步驟可以分成以下兩個階 段:(1) 應用於基地台細胞搜尋機制(cell search)之低功率 biased-number 相關器架 構設計,(2)應用於相位鎖相迴路技術 (phase locked loop) 之低面積改良式冗 餘算術座標旋轉演算法所設計之直接數 位頻率合成器設計。圖(一)所示為低功率 biased-number 相關器架構圖, CLKsys為系 統時脈訊號可以經由 MOD256 Selector 降頻二百五 十六分之一產生取樣時訊號 CLKs,同時亦可經由 Delay0 延遲元件產生相關器次系統的系統時脈 CLK。為了達成同步的目的, DelayO 元件延遲值可 以設定為(TADC+Tmul+TI/O)。CLK 時脈訊號經過 Controller1 產生 CLK0、CLK1、Shift/ Load。CLK0 主要是用以驅動 Register File Block。Shift/ Load 提 供給 Parallel-to-Serial Converter 和 PSC Generator 作 初始訊號載入功能,必須等待 CLKO 驅動的 Register File Block 完成動作後, Shift/ Load 才能產生,以 正確的將 Register File Block 輸出之訊號載入 Parallel-to-Serial Converter。CLK1 用以驅動 4-bit Parallel-to-Serial Converter 和 PSC Generator,所以 訊號必須等 Shift/ Load 到達後,才可開始驅動。 訊號經過以 Register 所串聯組成的 Moving Window Shift Register Block,將訊號儲存,此處將使用 Register File Block 來取代,以降低功率的消耗。此 部份使用 CLK0 來驅動, CLK0 的週期為 CLK 週期 的 256 倍。Register File Block 輸出連接到 4-bit Parallel-to - Serial Converter, 由 CLK1 所驅動,將 Register File Block 的輸出呈現序列式的一一輸 出,儲存在 Register(Reg\_B)。而 PSC Generator 亦 是由CLK1 驅動,輸出的PSC Code 存在DFF。Reg\_B 和 DFF 則由 CLK2 同步驅動輸入 BN Encoder 作運 算,CLK2為CLK1經過Delay2後的延遲訊號, Delay2 必須大於 4-bit Parallel-to -Serial Converter 和 PSC Generator 的延遲時間,才能保證 Register 所讀出的訊號為正確的訊號。經過 BN Encoder 運 算後之結果儲存於 Reg\_C,準備進入 BN Accumulator 作累加動作。經過 BN Encoder 有延遲 時間,因此CLK2再經過Delay3,得到延遲訊號 CLK3,用以驅動 Reg\_C,Delay3 必須大於 BN Encoder 得延遲時間, Reg\_C 才可讀到正確的值。 CLK3 同步驅動 Reg\_C 和 Reg\_D 讀出值進入 4-bit Adder 作累加,當 Adder 的 Cout 為'1'時,表示 Adder 已經滿了,驅動 8-bit Counter 計數。得到 Cout 需經 過 Adder 延遲時間,因此必須使得驅動 8-bit Counter 的時脈訊號比較晚到,才可正確計數。因此 CLK3 在經過 Delay4 產生 CLK3\_delay,用以驅動 Counter。經累加和計數完之訊號,將連接到 12-bit Register(Reg\_E),由 Controller2 產生的 Load 訊號來

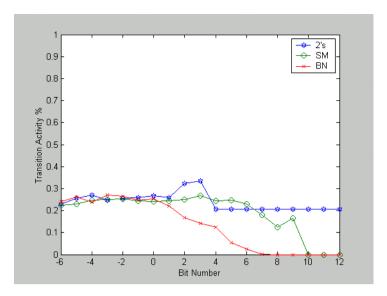

驅動讀出值。訊號由 Reg\_C 到 Reg\_E,最長的延遲時間為 T<sub>adder</sub>+T<sub>AND</sub>+T<sub>counter</sub>。應此輸出訊號 Load經過 Delay5 產生 Load\_delay,使得 T<sub>controller2</sub>+Delay5>T<sub>adder</sub>+T<sub>AND</sub>+T<sub>counter</sub>。才可正確讀出累加結果。正確讀出值後,即可清除 4-bit Register(Reg\_D)和 8-bit Counter。因此將 Load\_delay 在經過 Delay6 產生 Reset 訊號以清除 4-bit Register(Reg\_D)和 8-bit Counter。由圖(二)可以得知,2's、SM、BN 三種表示法中,BN的 Transition Activity 最低、SM 其次、2's 最高。

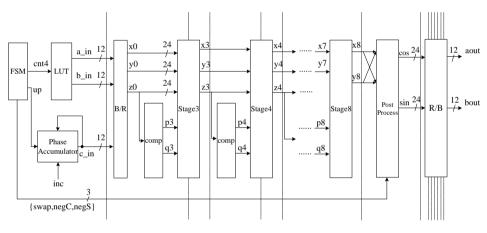

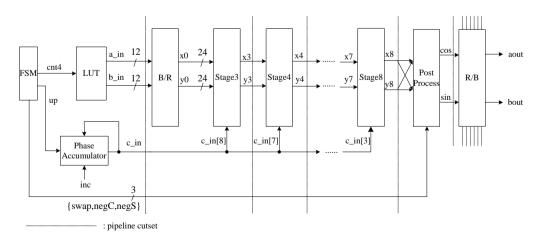

本計劃之另一重點為快數直接數位頻率合成 器(DDFS)之研究,我們採用8級Takagi的雙旋轉 CORDIC 架構[17]的 DDFS 來作改良,採用 Takagi 的 架構的原因,在於此架構為 RB 算術系統的 CORDIC, 能操作在較快的時脈,而其採用的演算法也使比例 係數為常數,降低了硬體實現的複雜性。我們提出 二種方法以減小原來 DDFS 的硬體面積分別達 30% 與 50%以上。第一個改良 DDFS 的方法是將 8 級的 CORDIC 旋轉運算移去 2 級以減少硬體使用,我們稱 之為 DDFS6 如圖(六)所示。可以將 CORDIC 的前面數 級移除,以縮小旋轉角度範圍的方式搭配查表儲存 起始點的座標,即可完成比雙旋轉法硬體面積較小 的 DDFS。此架構與雙旋轉法 DDFS 主要的不同在: (1) 多了一個儲存 8 字元(word)的查表器(Look Up Table, LUT);(2)CORDIC 的運算只剩原來的第三級 至第八級,所以可以旋轉運算的角度範圍變小了, 大約為原先的 1/4, 即 11.25 度, 每次連續轉 11.25 度後,即經由 cnt4 查表改變開始由第三級旋轉的 座標起始值,藉由四次的查表可達成45度的運算。 而 45~360 度的運算同樣是依照前述方式來運作。 因為 CORDIC 的級數變少,而且減少的前二級是各 有二階管線式(pipeline)的加法器,所以加法器減 少了八個,可有效減少硬體面積,並減少四個時脈 週期的延遲(latency)。第二個改良的方法同樣也 是使用 6 級的旋轉運算,但其旋轉的方式採用重新 編碼法(recoding method)[18],與CORDIC 稍微不 同,我們將此稱之為DDFS6 rec 如圖(七)所示。由 於重新編碼法的旋轉方式不同,所以其中查表器所 存的值和圖(六)中的值是不同,重新編碼法與 DDFS6 的旋轉角度不同,但其誤差非常小。在重新 編碼法中,每級旋轉方向的判斷,不需要額外計 算,相位累加器輸出的每個位元即控制了每級的旋 轉方向。DDFS6 的架構中, 第三級與第四級各有二 階管線式的加法器,而在重新編碼法的架構中,每 級只旋轉一次,不需要管線式架構,所以較 DDFS6 的架構減少了八個加法器,同時減少了二個時脈延 遲,而控制旋轉的訊號也不需要另外運算,所以也 減少了一些硬體使用。當雙旋轉法、DDFS6與 DDFS6\_rec 三種設計經過 Synopsys 合成工具,以 Avant!  $0.35 \mu m$  標準電路單元實現出不同 DDFS 的 架構之後,這三種架構皆可以在 350MHz 的操作頻 率內正常運作。

#### 四、 結論與討論

本計畫完成工作項目及具體成果主要包括以下數點:1.完成一全新低功率 biased-number 相關器之軟硬體設計,應用於WCDMA系統之

cell search。2.完成一全新低面積改良式冗餘算術座標旋轉演算法所設計之直接數位頻率合成器,應用於數位鎖相迴路。本計畫所發展出無線寬頻分碼多工用戶接收機低功率晶片並未在其他文獻出現過類似研究成果。

#### 五、 參考文獻

- [1]R. Prasad, W. Mohr, and W. Konhauser, Eds., "Third Generation Mobile Communication Systems", Boston, MA:Artech House, 2000.

- [2] 3GPP TSG/RAN/WG1, "Spreading and modulation(FDD)," TS 25.213 V3.0.0, Oct. 1999.

- [3] 3GPP TSG/RAN/WG1, "Physical layer procedures (FDD)," TS 25.214 V3.0.0, Oct. 1999.

- [4] OHG, "Harmonized glboal 3G(G3G) technical framework for ITU IMT-2000 CDMA proposal," Operator Harmonization Group, Beijing, June 1999.

- [5] K. Higuchi, M. Sawahashi, and F. Adachi, "Fast cell search algorithm in inter-cell asynchronous DS-CDMA mobile radio," IEICE Trans. Commun.,vol.E81, no.7, p.p.1527~1534, July 1998.

- [6] Siemens and Texas Instruments, "Generalized hierarchical Golay sequence for PSC with low complex correlation using pruned efficient Golay correlators," 3GPP Tech. Doc., Tdoc R1-99554, Cheju, Korea, June 1999.

- [7] Texas Instruments, "Comma free codes for fast PN code acquistion in WCDMA systems: A proposal for the UTRA concept-revised version," Tdoc SMG2 UMTS-L1 72/98, Paris, April 1998.

- [8] Ericsson, "New downlink scrambling code group scheme for UTRA/FDD," 3GPP TSGR1-541/99, July 1999.

- [9] Y.D.E. Wang and T. Ottosson," Cell search in W-CDMA," IEEE J. Select Area Commun. ,vol.18,no.8,pp.1470~1482, August 2000.

- [10]B.H.Kim and B. Gi Lee,"Distributed sample acquistion-based fast cell search in inter-cell asynchronous DS/CDMA systems," IEEE J. Select

- Area Commun., vol.18, no.8, pp.1455~1469, August 2000.

- [11]Y.Hanada, H. Higuchi, M. Sawahashi, and F. Adachi, "Fast cell search algorithm in idle mode for inter-cell asynchronous WCDMA mobile radio," IEICE Trans. Commun., volE83-B, no.8, August 2000.

- [12]S.Sheng and R.Brodersen, Low-power CMOS wireless communications: A wideband CDMA system design, Kluwer Academic Publisher, Boston, 1998

- [13]S. Sriran, K. Brown, and A. Dabak, "Low-power correlator architectures for wideband CDMA code acquistion,"The Thirty-Third Asilomar Conference: Signals, Systems, and Computers, vol.1, pp.125~129, 1999.

- [14] Charles Chien, Rajeev Jain, Etan G. Cohen and Henry Samueli, "A Single-Chip 12.7 Mchips/s Digital IF BPSK Direct Sequence Spread -Spectrum Transceiver in 1.2 im CMOS," IEEE Journal of Solid-State Circuits, Volume: 29, Dec. 1994, PP.1614-1623

- [15] Ken Chapman; Paul Hardy; Andy Miller; Maria George,"CDMA Matched Filter Implementation in Virtex Devices", http://www.xilinx.com

- [16]Keshab K. Parhi,"VLSI DIGITAL SIGNAL PROCESSING SYSTEMS: DESIGN AND IMPLEMENTATION", 1999.

- [17] N. Takagi, T. Asada, and S. Yajima, "Redundant CORDIC Methods with a Constant Scale Factor for Sine and Cosine Computation," *IEEE Trans. Computers*, vol .40, no.9, pp.989-995, Sept. 1991.

- [18] A. Madisetti, A.Y. Kwentus, and A.N. Willsion, Jr., "A 100-MHz, 16-b, Direct Digital Frequency Synthesizer with a 100-dBc Spurious-Free Dynamic Range," *IEEE J. Solid-State Circuits*, vol.34, No.8, pp. 1034-1043, Aug. 1999.

圖 (一) 低功率 biased-number 相關器架構圖

圖(二) 2's、SM、BN 的 Transition Activity 比較

: pipeline cutset

圖(三) 低面積 DDFS6 之架構圖

圖(四)低面積 DDFS6\_rec 之架構