# 金屬線及空氣低介電常數介電質前瞻性積體技術開發(2/2)

計畫編號: NSC 90-2215-E-009-046

執行期限:90年08月01日至91年07月31日

主持人:張國明 國立交通大學電子研究所

計畫參與人員:楊知一 王敬業 陳弘育

林銘崎 張昱勳 陳宥霖 國立交通大學電子研究所

#### 一、中文摘要

當積體電路的尺寸越做越小時,元件 與元件之間的傳輸延遲已開始主導整體系 統的效能。金屬內連線的阻抗時間延遲將 限制了元件操作速度的表現。兩個最主要 的因素在於金屬線的電阻與金屬連線間的 電容。特別是在於金屬線寬加上線距小於 0.25 微米時,很長的金屬連線造成龐大的 寄生電容。更甚者,功率損耗也是一個嚴 重的問題,像是在於微處理器以及射頻積 體電路。藉著使用低介電係數材料以及低 電阻係數的金屬將可以有效的降低元件的 阻抗延遲。為使傳輸速度加快,導線阻值 與導線間介質的介電係數必須降低。在降 低導線阻值方面,近年來最紅的莫過於銅 導線製程。日前在生產線上,銅金屬內連 線製程已經成功的被開發製造應用在現今 的 0.13 微米製程晶片上,有效的降低導線 間的電阻值且確實提高晶片的操作速度。 尤以 IBM 的銅晶片更廣為人知。而降低導 線間電容的方法則為使用低介電質材料。 估計在西元 2004 年之前, 必須將介電係數 介於2.0~2.2之低介電係數材料成功的導入 超大型積體電路晶片的後段製程中。國際 半導體協會之半導體發展里程表(Roadmap) 指出, 積體電路後段製程的低介電係數絕 緣介電質製造技術將在西元2005年遭遇莫 大的瓶頸。電子材料可能很難合成出介電 係數低於 2 且可應用於半導體製程中的絕 緣介電質。

現今各種預測半導體發展的預測里程表(Roadmap)皆指出也許空氣將於未來應用於極大行積體電路上。不過,該如何實現,至今尚無定論。其中以空氣為擁有最

低介電值物質。不過如何使空氣介質應用 於積體電路之上,實為半導體界之一重大 挑戰。

本實驗室即提出以空氣作為後段金屬連線 與連線(Line to Line)之間的絕緣介電質,而 金屬線層與層(Layer to Layer)之間則仍由 固態低介電係數絕緣介電質充填。如此, 將可更進一步有效地降低後段金屬內連線 的阻抗值,進而提昇了訊號傳輸的速度。

本計劃已在過去的兩年內執行。第一年度利用倒置製程晶片的方法使欲形成之薄膜位於金屬線與其空氣隙的下方,以此規避傳統製程中沉積其他薄膜時須將薄膜堆疊於固體之上的限制,而空洞便在薄膜成型後形成。並計算形成空洞的必要因素,分析表面張力,大氣壓力及重力,探討何種條件搭配,方能使空洞製作達到百分之百的可重複性。第二年度我們發展了多重空洞金屬連線的製程。搭配銅金屬製程與空氣隙,並透過一些模擬程序驗證他的可行性。

關鍵詞:空氣隙,空氣介質,低介電材料, 電阻電容遲延

#### **Abstract**

As the advanced ULSI has continued to shrink, the transmission delay between devices dominates the performance of the whole circuit system. The RC time delay of interconnects will limit the device speed performance. The two components of the

delay arise from the resistance of the metal interconnects and the capacitance of the inter-metal dielectric. This is especially true in devices with a wiring pitch less than 0.25  $\mu$  m, which typically has much higher capacitance due to their long wiring length. Furthermore, power consumption is also a concern for high-speed device; such as microprocessor unit or radio frequency integrate circuit. By using materials with low dielectric constant (low-k material) and low resistivity metal can reduce the RC time delay in devices. In order to improve the transmission speed, the resistivity of metal lines and the inter-level dielectric between metal lines must be decreased. In the field of decreasing resistivity of metal lines, the popular method is copper process in recent year. In the past few days, the 0.13  $\mu$  m production line has developed the copper process successfully. It's really decrease the resistance of interconnect metal effectively and indeed improve the operating frequency of the integration circuit chip. Especially, the "Copper Chip", which is developed by IBM, is well known. And the method of decreasing capacitance between the inter metal lines is to use low dielectric constant materials as the inter-level dielectric. In estimation, we should apply the low-k (2.0

2.2 dielectric constant) materials to the back-end process in ULSI before A.D 2004. The International Technology Roadmap for Semiconductors (ITRS) point out that the low-k materials technology in back-end process of ULSI will meet a difficult bottle-net. We could not synthesize the electronic material with the dielectric constant below 2 for semiconductor industry.

So far various roadmaps in ULSI indicate that maybe air will be used in the future owing to with the lowest dielectric constant. However, how to apply air in the ULSI is still a mess to all the engineers in the semiconductor field. The research project in our laboratory is using air as insulator between inter-metal lines, and the low-k solid thin film is still being the insulator between

inter-layer metal. We believe that it will reduce the impedance of interconnection in the back-end process and really promotion the speed of signal transformation.

This project had been executed in passed two years. In the first year, we developed an upside-down technique to avoid limitation that a thin solid film must be deposited on solid body. Thus, we can form a thin insulating layer above the metal lines. We analyze the effect of the surface tension, atmosphere pressure and gravity on the air gap formation. We also study the factors dominating the formation of the air gaps and the parameters consideration to get the air gaps processing reliability. In the second year, we developed the multi-level air gap metallization. We combined the copper metallization and air gap in the back-end process, and identified the possibility through some simulation module.

Key words: air gap, air dielectric, low dielectric constant materials, RC time delay.

## 二、緣由與目的

由於國際半導體協會在半導體技術發展里程會議中明確的共識指出,在未來2003-2008 年積體電路技術在技術進步上將遭遇到前所未有的困難與挑戰。電路的後段金屬內連線的技術上,依照現有的材料技術將無法解決未來在積體電路內的信號傳輸阻抗延遲的問題。

為了繼續提高積體電路的積集度,金屬線的截面積也必須越來越小,這將造成電流密度的需求必須變大,而且導線的電阻率也將因為截面積的縮小而加大,也因此國際半導體協會認為將來的技術中,包附金屬線外圍的阻障層厚度將會降到零才有辦法滿足未來元件電性上的需求。另外,就目前的金屬傳輸線都是以銅金屬作為傳輸線,銅金屬本身具有高度的擴散

性,若沒有阻障層包覆銅金屬線,積體電路將沒有可靠度可言。這將是一個無解的 難題。

本計劃構想便是為這國際間認定無解的難題提出一個解答以作為下世代的積體電路技術。因為,在積體電路的信號傳輸延遲是由電路上的傳輸阻抗所決定。傳輸阻抗包括了傳輸線的電阻值與傳輸線之間的容抗值。想要繼續縮小金屬傳輸線的截面積是不可能的,這將大幅提升金屬傳輸線上的電阻值。因此較有可能的方法便是朝金屬傳輸線之間的容抗值著手。

本計劃提出以空氣作為金屬傳輸線之間的絕緣介電質層,而層與層之間則仍然沿用低介電常數物質。因為空氣具有最低的介電常數值。另外也因為銅金屬線仍然被阻障層牢牢的包覆,在可靠度上的條件並不因此改變;在相同的電性位準下也不需要縮小金屬傳輸線的截面積。如此將可以為下世代的積體電路發展新一代的製造技術。

## 三、結果與討論

#### 研究方法:

關鍵詞:二氧化矽支柱,底板,預塗層, 常溫液態低介電材質(Low-K material)。

尺寸規格:二氧化矽支柱:1000nm

銅(Cu)金屬線薄膜厚度:500nm

銅(Cu)金屬線寬:500nm 銅(Cu)金屬線間隙:800nm

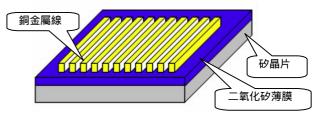

首先我們先在欲佈局金屬線的矽晶片上成長二氧化矽(SiO<sub>2</sub>)薄膜以作為絕緣基板,此晶片即為元件晶片。在此,我們揚棄去年的製程步驟,不再以每一個晶粒四周之氮化矽(Si<sub>3</sub>N<sub>4</sub>)作成支柱。直接將銅金屬線以大馬士製程(Damascene process)佈局在晶粒中央。如下圖一。此時銅金屬線四周皆覆蓋著擴散阻障層。

圖一:金屬線元件於二氧化矽薄膜上。

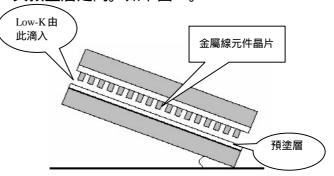

接下來我們取另一塊晶片作為底板, 我們在這塊底板上成長二氧化矽支柱來代 替原先在元件晶片上的氮化矽支柱。接下 來在此底板上旋塗某種可流動性的材質 (預塗層),並將此預塗層烘乾。然後再將金 屬線元件晶片倒反過來,倒置在底板的預 塗層上。接著再將常溫液態低介電材質滴 入金屬線與預塗層之間,藉由重力以及液 體表面張力的力量使之均勻分布於金屬線 與預塗層之間。如下圖二。

圖二:金屬線元件倒置於底板預塗層上。

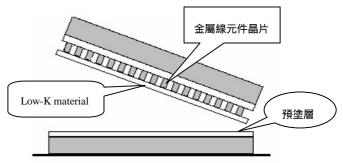

然後等到常溫液態低介電值層凝固後,再經由熱能使得低介電值層與預塗層之間因為彼此的相變化而產生低附著係數特性而分離。如下圖三。

圖三:以熱能將元件與底板預塗層分離。

完成了金屬連線與空氣隙的結構後,以 HP4156 進行電性上的量測;並與一般以 low-k 絕緣的金屬線比較其絕緣性與漏電 特性。另外我們也發展多層空氣隙與金屬 連線結構的製程步驟,並以電腦模擬其可行性。

積速度較慢,但均勻度相對較 高。

#### 研究進度:

- (一) 預塗層的材料選擇,至今仍未找到最令人滿意恰當合適的材料。這方面可能必須藉助材料研究相關方面人員參與。我們現階段分別以不同濃度的光阻與膠水來當作預塗層。試以不同應定以得到不同厚度的預塗層的預塗層將會對溫度有不同的熱膨脹截面應力的產生。並試以不同的溫度預烤,預烤溫度介於室溫至攝氏50度。然後再將金屬線元件倒置予以烤乾的預塗層上。

- (二) 我們試以不同的傾斜角度與不同濃度的常溫液態低介電值材料,以研究重力與表面張力對液態低介電值材料的流體加速特性。結果我們發現重力效應對空洞形成的影響幾乎可以忽略。由於金屬層與預塗層的間隙僅有500nm,所以液態低介電值材料的流速度完全由表面張力決定。而決定表面張力的因素主要來自於流體濃稠度以及與金屬線的接觸截面積。也就是以及與金屬線的接觸截面積。也就是說,金屬線寬度越寬,以及金屬線間隙越小,越容易形成平整且覆蓋面積完整的低介電值薄膜與空洞。

- (三) 因為氮化矽支柱的沉積與蝕刻皆不符合製程上的特性需求。所以我們改為在底板晶片上沉積或成長二氧化矽薄膜,再以 BOE 溶液濕式蝕刻來形成二氧化矽支柱。一則大幅縮短支柱製程步驟的時間以及克服了蝕刻氮化矽時所遭遇到光阻脫落的問題。

### 同時,我們發現

- (a) 以 PECVD 沉積二氧化矽,沉 積速度非常快,但均匀度不是 那麽好。

- (b) 以 ECRCVD 沉積二氧化矽,沉 積速度非常快,同時均勻度也 相當好。

- (c) 以濕式氧化成長二氧化矽,沉

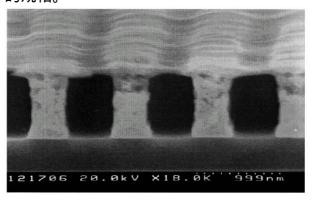

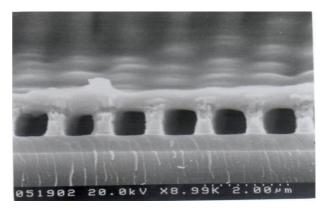

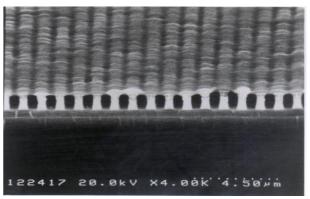

- (四) 單層空氣隙金屬連線結構在小面積範 圍內已經順利完成。其中,金屬線的 佈局是以 Damascene 製程來達成。我 們先旋塗上某種特殊 Polymer, 該種特 殊 Polymer 可以在攝氏 350 度以上被 氣化。然後再蝕刻出銅金屬線欲佈局 處的溝渠,分別以 CVD 與 PVD 的方 式沉積蝕刻停止層與金屬擴散阻障 層,再以電鍍銅的方式將銅金屬沉積 在晶片上, 然後以 CMP 磨掉不要的銅 金屬,留下溝渠內的銅導線,再沉積 一次金屬擴散阻障層,然後將溝渠銅 金屬以外的金屬擴散阻障層蝕刻掉, 再加以攝氏 400 度的高溫將該種特殊 Polymer 氣化掉。如此便可順利的製造 出被金屬擴散阻障層完整包覆的銅金 屬導線。因為銅金屬導線具有高擴散 能力,所以一定要有金屬擴散阻障層 來阻擋銅擴散。否則元件將沒有可靠 度。

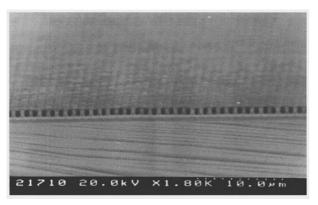

- (五) 另外,為了發展多層空洞金屬連線技術,我們也藉助了平面旋轉塗佈機來將低介電係數材料旋塗在倒置晶片中以做為金屬層與金屬層之間的介電絕緣物質。配合銅金屬的擴散阻障層,以及化學機械研磨的技術,來達到平坦化的成果。

#### 研究結論:

當我們要在絕緣電介質 SiO<sub>2</sub>上面形成 金屬線時,以濕式蝕刻的方式無法形成良好的高深寬比空洞。如此在深次微米元件 製程的應用中,由於金屬線的側向蝕刻,將直接影響金屬線寬的可靠性。而乾式蝕刻也會對光阻薄膜下方的金屬產生些微的內切(Under Cut)。在金屬線線寬與金屬線間距大於 500nm 時,對鋁金屬線的些微內切,仍是可以接受的。但在現今與未來的深次微米製程,金屬線寬與間距皆小於200nm 以下時,不論是鋁金屬或者是銅金屬,對金屬的乾式蝕刻將不再適用。在未

來 的 所 有 積 體 電 路 都 一 定 要 使 用 Damascene 製程觀念來形成金屬線以達到 深次微米的規格。

為了盡量減少對元件晶片的熱製程傷害,我們將支柱改為二氧化矽,並改成沈積在預塗層晶片上。我們可以也藉由一些高密度電漿化學氣相沈積(HDP-CVD)的設備在攝氏 300 度以下來快速沈積氮化矽薄膜。尤其以電子迴旋共振化學氣相沈積(ECR-CVD)最為成功。因為他可以在很短的時間內形成均勻度良好的薄膜。即使在一般的 PECVD 也可以迅速的達到相同的效果。而這些設備都是目前半導體廠內普遍擁有的設備。也就是說本計畫完全是以生產線上的相容性考量的。

對於低介電係數材料的蝕刻,一般的 蝕刻設備的製程溫度大都分佈在攝氏 250 , 但由於本計劃是將空氣介質應用在極 大型積體電路(ULSI)中的後段內連線中,並 不適合在高溫之中進行。能將製程溫度控 制越低溫,對元件的熱傷害將會越小。尤 其以電子迴旋共振化學氣相沈積 (ECR-CVD)最為成功。因為他可以在攝氏 30 以下完成對低介電係數絕緣材料的蝕 刻。在如此低的製程溫度下,將可對前端 製程的熱效應傷害降低到最小的程度。尤 其是在 0.13 微米的元件裡,熱傷害對 MOSFET 的源極與汲極的摻雜接面深度的 重新擴散分佈效應是非常嚴重的。而在後 段製程中,熱效應也將增強銅金屬對擴散 阻障層的擴散能力。這些都是不能接受的。

在金屬線下方的的低介電值材料,在 第一年度時曾經是相當大的瓶頸。我們必 須調配出熱膨脹係數與差異較大的預塗層 材料,且其與低介電係數絕緣材料的附著 係數必須是相當低的。在這種條件下才能 使得旋塗進去的低介電係數絕緣材料與下 方的預塗層順利分離。這層預塗層可以是 一種與低介電係數絕緣材料之間的附著係 數很低的某種特殊合金金屬薄膜。

金屬線層與層(layer to layer)之間的低

介電係數絕緣介質除了藉以重力與表面張力的方式來形成,我們也多次以旋塗的方式做出單層空氣隙金屬內連線結構。雖然我們已經順利的完成單層空氣隙金屬連線結構(如下圖示),但囿於設備的精密度與制度的限制,沒有先進的旋塗設備,沒有先進的旋擊是一個大大面積上完過模。但我們透過程可以確信該製程的可行性,與正確認金屬線間的電容值確實制到空氣的崩潰電場強度與漏電流特性,真正確認金屬線間的電容值確實能符合國際半導體協會所公佈的製程需求里程表中所列的規格。

### 四、計畫成果自評

本研究計劃在向國科會提案之前就已經做了許久的相關研究,歷經多年與多人的努力參與。雖然距離實際商業化應用仍有一段距離,但因為先期的研究成果已經在國際學術期刊上獲得相當的認可(參考文獻-5),並由於現階段商業積體電路的技術面類越來越緊縮,而使得本研究團隊的技術可行性相對的有逐步明朗化與迫切需要的趨勢。本研究計劃的技術流程已經被本研究群所開發出來,相信將為下世代的積體電路製造技術帶來革命性的轉變。但是,仍然有許多關鍵步驟有賴於全新設計的製程設備來支援才有辦法達成。

## 五、參考文獻

- (1) M. B. Anand; M. Yamada; H. Shibata, "NURA: A Feasible, Gas Dielectric Interconnect Process", Symp. On VLSI Technology, P.82-83, June 1996.

- (2) Ben Shieh; Krishna Saraswat; Mike Deal; Jim Mcvittie, "Air Gaps Lower K of Interconnect Dielectrics", Solid State Technology, P.51, February 1999.

- (3) Anand, M.B.; Yamada, M.; Shibata, H. "Use of gas as low-k interlayer dielectric in LSI's: Demonstration of feasibility", Electron Devices, IEEE Transactions on , Volume: 44 Issue: 11, Nov. 1997

Page(s): 1965 -1971

(4) "Intermolecular & Surface Forces"

Jacob Israelachvili Academic Press P.114

- (5) Kow-Ming Chang; Ji-Yi Yang; Lih-Woen Chen, **A novel technology to form air gap for ULSI application,** IEEE Electron Device Letters, Volume: 20 Issue: 4, April 1999, Page(s): 185 –187

- (6) Ueda, T.; Tamaoka, E.; Yamashita, K.; Aoi, N.; Mayumi, S., A novel air gap integration scheme for multi-level interconnects using self-aligned via plugs, VLSI Technology, 1998. Digest of Technical Papers. 1998 Symposium on , 1998, Page(s): 46 -47