# 行政院國家科學委員會補助專題研究計畫成果報告 \*\*\*\* **※ ※ ※ ※** 無線通訊之時空域信號處理(2/3) Space-Time Signal Processing for Wireless **※ ※** Communication (2/3)**※** \* \* \* \*\*\*\*\*\* 計畫類別:□個別型計畫 整合型計畫 計畫編號: NSC 89-2219-E-009-036 執行期間:89年8月1日至90年7月31日

計畫主持人: 林大衛 交通大學電子工程系所 教授

本成果報告包括以下應繳交之附件:

□赴國外出差或研習心得報告一份

□赴大陸地區出差或研習心得報告一份

□出席國際學術會議心得報告及發表之論文各一份

□國際合作研究計畫國外研究報告書一份

執行單位:國立交通大學電子工程學系

中華民國八十九年十月三十一日

# 行政院國家科學委員會專題研究計畫成果報告

# 無線通訊之時空域信號處理(2/3)

### Space-Time Signal Processing for Wireless Communication (2/3)

計畫編號: NSC 89-2219-E-009-036 執行期限: 89年8月1日至90年7月31日 主持人: 林大衛 交通大學電子工程系所 教授

計畫參與人員: 周志昇、林郁男、何健豪、賴侑呈、張佑榕 交通大學電子工程系所

#### 一、摘要

關鍵詞:寬頻分碼多重進接、時空維特比等化、時空域信號處理、訓練數列、平行式干擾消除、連續式干擾消除、數位訊號處理器實現

#### Abstract

We research into techniques for efficient usage of wireless channels in wireless transmission systems, including space-time processing signal and implementation, with emphasis on WCDMA uplink transmission. On general space-time signal processing, we research into the design of space-time Viterbi equalizer and its performance. We propose a Newton-like fast method to search for optimal training sequences. On space-time signal processing WCDMA, consider we parallel interference cancellation (PIC) successive interference cancellation (SIC), as well as their combination with antenna array signal processing. On DSP implementation, we attempt wireless channel simulation using the DSP board and PIC under an antenna array. Under simple channel conditions, the

execution speed can support real-time operation.

**Keywords:** WCDMA, Space-Time Viterbi Equalization, Space-Time Signal Processing, Training Sequence, Parallel Interference Cancellation (PIC), Successive Interference Cancellation (SIC), DSP Implementation

#### 二、計畫緣由與目的

本計畫研究有效地使用無線通道之技術,含時空域信號處理之方法及使用 DSP 遂行其實現之方法,其中著重寬頻分碼多重進接(WCDMA)系統之上鍊傳輸。其一主要目的在與其他子計畫共同完成一個 WCDMA 上鍊傳收系統之設計與 DSP 實現。本計畫本年度之研究項目有三:一是一般時空域信號處理技術,二是 WCDMA上鍊傳輸之時空域信號處理技術,三是 DSP實現。

在 WCDMA 上鍊傳輸之時空域信號處理方面,我們考慮平行式干擾消防(PIC)與連續式干擾消除(SIC),及其與天線陣列信號處理之接收器。首先,在 PIC 及其與所處理之接收器。首先,在 PIC 及其與同樣處理之結合方面,我們研究各種不過與人類人類,我們們不會的影響可以 PIC 增加的上確率。其次,在 SIC 方面的大學的工作。其次中的用戶面的大學的干擾量,因此,傳統的等功率分配對

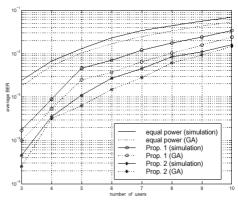

其並非最佳的功率分配機制。基於最小化 平均錯誤率和最小化最大錯誤率的原則, 我們研究合適的功率分配機制。

在DSP實現方面,我們用晶片板試做無線通道模擬及使用天線陣列之平行式干擾消除。我們並研究傳輸端資訊碼框組合之實現及傳輸端與接收端之方根升餘弦(SRRC)濾波器之定點(fixed-point)實現。

# 三、結果與討論

#### A. 一般時空域信號處理

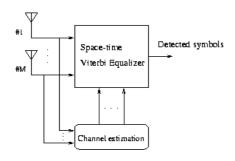

在時空域信號處理方面,我們使用一個時空域維特比(Viterbi)等化器當接收端的信號處理核心,如圖一所示。

在上一年度,我們設計了一個最小誤差 量的訓練數列(min-norm training sequence) [1],[2],使通道估計的誤差能減到最低。由 電腦模擬無線傳輸的結果也驗證了數列的 優點。但是這種數列,到目前為止仍無法 經由規則的方法產生,只能直接對大量或 所有可能的數列作搜尋而得。當數列長度 不大時,這不會造成太大的問題,但是當 數列長度比較大時,所有可能的數列就是 一個很龐大的數目。如我們所用的數列長 度是 29,如果以 QPSK 為調變符碼時,所 有可能的數列將高達 428個。要對如此多的 數列作搜尋,可能要花上數個月的時間, 所以我們發展出一套類似牛頓法的搜尋方 式。由實驗發現:大約只需要一天的時間, 就找到相當不錯的數列。雖然這種搜尋方 式並無法保證找到最佳數列的時間,但是 隨著搜尋時間增加,我們可以保證所得到 的數列會越來越接近最佳,也可以知道所 找到的數列與與最佳數列之效能差距[3]。

下面的數列是我們到目前為止找到長 度為29的最佳 QPSK 數列。

#### B. WCDMA 上鍊傳輸之時空域信號處理

本部份研究主要考慮平行式干擾消除 (PIC)和連續式干擾消除(SIC),及其分別與 天線陣列信號處理結合的效果。

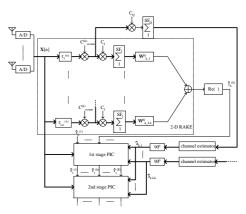

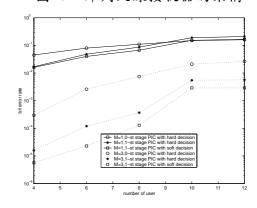

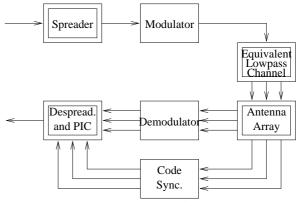

在結合陣列天線與PIC的部份,我們研究在其中使用不同之決策方法的影響。這些決策方法可分為硬式及軟式兩大類。對NMIC[5]等軟式決策法,我們推導出了適用於天線陣列及多重路徑下的決策曲線形式。完整的接收器架構如圖四所示。圖五是部份在3GPP規格下的模擬結果,以位元錯誤率為評量的標準。其中所謂 hard decision 即為標準的 PIC,而 soft decision則為 NMIC 架構。從模擬的結果可看出,以天線陣列提高初始正確率,再搭配 PIC的接收器架構應是不錯的選擇[6]。

從硬體實現的角度來看,PIC 接收器是以 hard-decision 型式者為最簡單實用,但至今未有對其效能之完整分析。我們嘗試進行分析,並已有初步結果[7]。

# C. DSP 實現

我們採用二種 DSP 板遂行實現。一是 Blue Wave Systems 的 PCI6600, 其上裝置 德州儀器公司(TI)的 TMS320C6701 浮點 (floating-point) DSP chips 二顆。它是透過 PCI 匯流排和 PC 做連接,由 PC 控制 DSP 晶片的運作,包括程式的載入和執行,並 可由 PC 端做運算結果的驗證。兩顆 DSP 之間的資料傳輸可透過共用記憶體(shared memory)來達成。由於過去的使用經驗,我 們對此板較熟悉。但其通訊能力較差,有 礙總計畫欲達成之整合。故我們另亦採用 Innovative Integration 公司(II)的 Quatro6x, 上面配載 4 顆 TMS320C6701 DSP。它也是 透過 PCI 匯流排和 PC 做連接,另外在 debug 的階段,還需要利用同樣使用 PCI 匯流排的 JTAG 板,以方便對於運算結果

的驗證。Quatro6x 最大的特色,在於四顆DSP 之間和跨板的溝通機制使用了快速的FIFO。同一塊版子上的任意兩顆DSP之間都有FIFO Link 連接,所以在一塊板子上,總共有6個FIFO Links。而板子間的溝通是使用FIFO Port,不過只有三個 DSP (DSP\_1-DSP\_3)有此機制,另外一顆 DSP (DSP\_0)則使用 PCI 和外界溝通。

目前已完成的實現,係採用 PCI6600。 以下簡報此結果。目前已實現的是簡單的 展頻運作、基頻無線通道模擬器、以及含 天線陣列處理功能的 PIC 接收器(時空 PIC 接收器)。展頻和通道模擬部分使用一顆 DSP,而 PIC 接收器則使用另一顆。系統 架構如圖七,其中雙線之方塊為本計畫目 前已有簡單實現者。

在PIC接收器部分,為求減低運算量,目前僅在其 initial stage (即 rake receiver 的部分)用簡單的指數平均法做通道估計,在PIC部分則沿用之。目前做到的處理速度,在僅有 initial stage下,一天線一路徑時可達 4.1 Mcps,三天線各三路徑時為 1 Mcps;在有一級 PIC下,一天線一路徑時為 0.406 Mcps,三天線各三路徑時為 0.082 Mcps。可見也是在極簡單的情況下才能達到真時執行的速度。

以下簡單分析 DSP 的運算能力,以了解其提供多少空間供較複雜的通道模擬與時空 PIC 接收器作真時執行之用:我們所用的 DSP 工作在 167 MHz。故每 chip 平均可分得約 43.4 cycles。若是六個運算單元都隨時平行在工作,每 chip 可分得 260 指令,其中含 86.8 個乘法指令。我們所模擬的通道是時變的,且所有的數值都是複數。每一複數乘法需四個實數乘法加二個實數加法。所以在乘法器 100%利用的狀況下,最多可實現約 20 個 taps 的通道。不過由於

DSP 提供的 data routing 未必盡能符合通道模擬之所求,實際上能做到的 tap 數應該會是數倍以下。時空 PIC 方面,通道估計以外,以解展頻與再展頻所需的速度最快,而總運算量則約與 KAP 成正比,其中 K 為使用者數目,A 為天線數目,P 為每天線路徑數目。經驗顯示,C 程式在經過編譯後,往往只會同時用到兩個左右的 DSP 運算單元。要增加處理速度,就要增加平行度。

### 四、計畫成果自評

研究內容與原計畫相符程度:大體相符,差異之處在時空信號處理演算法的內容。此種差異,在研究的過程中常會出現。相符程度80%。

達成預期目標情況:創新之發現、理論 之推導、計算機模擬軟體之建立、實驗系 統之初步建立、人才培育。

成果之學術與應用價值等:學術價值 高,部分成果已公開發表。應用價值方面, 最重要者為 DSP 實現之成果。將於下年計 畫中繼續演算法之研究與 DSP 實現。

綜合評估:本計畫獲得一些具有學術與應用價值的成果,符合三年期總計畫之WCDMA上鍊傳收系統研究與DSP實現之目標,並達人才培育之效。自評為「佳」。

#### 五、參考文獻

- [1] C.-S. Chou and D. W. Lin, "Training techniques of space-time Viterbi equalizer for high speed modile communication," in *Proc. IEEE Int. Symp. Circuits Syst.*, vol. II, pp. 89-92, May 2000.

- [2] C.-S. Chou and D. W. Lin, "Signal design and receiver dimensioning for space-time Viterbi equalization," *IEE Proc.-Commun.*, vol. 148, no. 3, pp. 132-138, June 2001.

- [3] C.-S. Chou and D. W. Lin, "Training sequence and memory length selection for space-time Viterbi equalization", *J. of Communications and Networks*, vol. 2, no. 4, pp.361-366, Dec. 2000.

- [4] C.-S. Chou, "Signaling and receiving techniques for wireless communications," Ph.D. dissertation, Dept. Electronics Engineering, National Chiao Tung University, July 2001.

- [5] D. Divsalar, M. K. Simon, and D. Raphaeli, "Improved parallel interference cancellation for CDMA," *IEEE Trans. Commun.*, vol. 46, no. 2, pp. 258-268, Feb. 1998.

- [6] Y.-N. Lin and D. W. Lin, "Performance comparison of several parallel interference cancellation techniques under the 3GPP WCDMA specifications," in *Proc. Asia Pacific Conf. Commun.*, pp. 257-261, Nov. 2000.

- [7] Y.-N. Lin and D. W. Lin, "Analysis of hardlimiting parallel interference cancellation (PIC) for synchronous CDMA communication,"

- submitted to IEEE Int. Symp. Circuits Syst. 2002.

- [8] Y.-N Lin and D. W. Lin, "On optimal power distribution for successive interference cancellation for wideband CDMA," in Proc. IEEE Workshop Signal Processing Advances Wireless Commun., pp. 38-41, Mar. 2001.

- [9] J.-H. Her and D. W. Lin, "DSP implementation of CDMA receiver based on parallel interference cancellation," in *Proc. Int. Symp. Commun.*, Tainan, Taiwan, ROC, Nov. 2001.

- [10]J.-H. Her, "DSP implementation of CDMA receiver based on parallel interference cancellation," M.S. thesis, Dept. Electronics Engineering, National Chiao Tung University, June 2001.

## 六、圖表

圖一:時空域維特比等化器架構

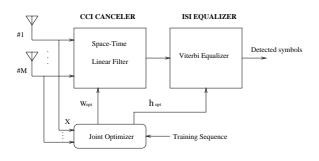

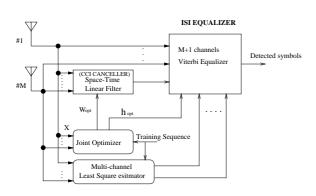

圖二:雙級混合式時空域接收器架構

圖三:結合時空濾波與時空域維特比等化 器的雙級混合式接收器架構

圖四: 陣列天線接收器的架構

圖五:不同 PIC 架構位元錯誤率之比較

圖六:SIC 在不同功率分配方法下之表現

圖七:DSP 實現之系統功能