# K-Band CMOS Sub-Harmonic Resistive Mixer With a Miniature Marchand Balun on Lossy Silicon Substrate

Hung-Ju Wei, Student Member, IEEE, Chinchun Meng, Member, IEEE, Po-Yi Wu, and Kuan-Chang Tsung

Abstract—A K-band sub-harmonically pumped resistive mixer is demonstrated using standard 0.13  $\mu$ m CMOS technology. A miniature Marchand Balun is integrated with the resistive mixer to generate equal amplitude and out-of-phase signals for mixer's local oscillation (LO) port directly on the lossy silicon substrate. The sub-harmonic resistive mixer with the integrated Marchand balun has conversion loss of 11–12 dB at  $f_{\rm IF}=100$  MHz and  $P_{\rm LO}=7$  dBm for RF frequencies from 18 to 26 GHz. The LO-RF and LO-IF isolations are approximately 30 and 33 dB, respectively.

Index Terms—Marchand balun, monolithic microwave integrated circuit (MMIC), sub-harmonically pumped resistive mixer (SPRM).

#### I. INTRODUCTION

POR a high-speed communication system, the mixer plays an important role for the frequency conversion. To alleviate the burden of designing a local oscillator at high frequencies, the sub-harmonic mixer topology is proposed [1]. The sub-harmonic mixer prevents the self-mixing problem caused by the local oscillation–radio frequency (LO–RF) leakage by operating the LO frequency at half of the RF frequency. An active Gilbert mixer requires a high dc power consumption for the specific conversion gain and speed. Therefore, the passive mixer without dc power consumption becomes an attractive candidate for high frequency applications. However, most sub-harmonically pumped resistive mixers (SPRM) are implemented in III/V semiconductor technologies over the past years [2]–[6].

As the CMOS device continuously scales down to the deep sub-micrometer regime, the cut-off frequency,  $f_T$ , obviously already catches up with and even exceeds that of III/V technologies. More and more CMOS integrated circuits have been realized at microwave and millimeter-wave frequencies. For instance, the first CMOS drain-pumped resistive mixer was demonstrated at 30 to 40 GHz with a low conversion loss of 4.6 dB [7] and the resistive mixer using gate-pumped topology has high linearity performance from 26.5 to 30 GHz [8]. However, these are fabricated in the 90-nm silicon-on-substrate (SOI) CMOS technology, which can reduce the substrate loss

Manuscript received June 18, 2007; revised September 6, 2007. This work is supported by the National Science Council of Taiwan, R.O.C., under Contracts NSC 96-2752-E-009-001-PAE and NSC 95-2221-E-009-043-MY3, by the Ministry of Economic Affairs of Taiwan under Contract 95-EC-17-A-05-S1-020, and by the MoE ATU Program under Contract 95W803.

The authors are with the Department of Communication Engineering, National Chiao Tung University, Hsinchu, Taiwan 300, R.O.C. (e-mail: ccmeng@mail.nctu.edu.tw).

Digital Object Identifier 10.1109/LMWC.2007.911991

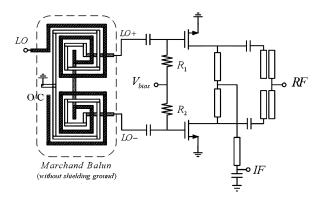

Fig. 1. Schematic of 0.13  $\mu$ m CMOS SPRM with integrated Marchand balun.

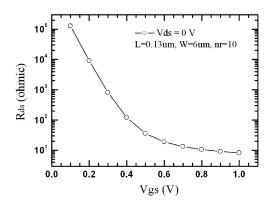

Fig. 2. Simulated  $R_{\rm ds}$  as a function of  $Vg\,s$  at  $V\,ds=0$  V for the NMOS devices used in the SPRM.

and coupling at the cost of higher fabrication price. For a low cost requirement, a 9–31 GHz source-pumped resistive mixer is first demonstrated in 90-nm standard CMOS process [9].

In this work, a single balanced structure with gate-pumped topology is employed to achieve better isolation and higher linearity. The symmetry of the balanced structure renders the inherent ability of rejecting unwanted signals. Therefore, the single-to-differential component significantly affects all kinds of specifications, such as the LO–RF isolation and the minimum conversion loss. It is difficult to generate a pair of equal amplitude and opposite phase signals at high frequencies for the active baluns. Thus, the passive broadband Marchand balun is explored in this work. Most miniature Marchand baluns are designed on the semi-insulating, high-resistive substrate or ground shielding plane [10] in the past. In this letter, we report a SPRM with a Marchand balun directly on the lossy silicon substrate [11]. The implementation method is compatible with

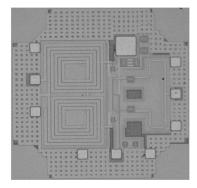

Fig. 3. Photograph of the 0.13  $\mu\mathrm{m}$  CMOS SPRM with the integrated Marchand balun.

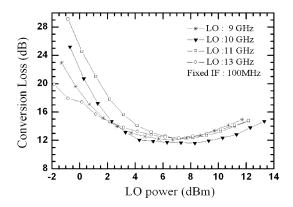

Fig. 4. Measured conversion loss versus LO power for the 0.13  $\mu m$  CMOS SPRM with the integrated Marchand balun.

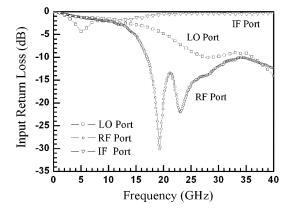

Fig. 5. Return loss of the 0.13  $\mu$  m CMOS SPRM with the integrated Marchand balun.

the standard silicon process and the Marchand balun has small size out of higher effective dielectric constant when compared with other published resistive mixers [12].

## II. CIRCUIT DESIGN

Fig. 1 shows the schematic of the SPRM using the standard 1P8M 0.13  $\mu$ m CMOS technology. The passive down-converter basically consists of two identical NMOS devices, a miniature marchand balun and RF/IF filters.

For the SPRM, the individual channel resistance is pumped by the LO signal in the anti-phase way. Because of the parallel

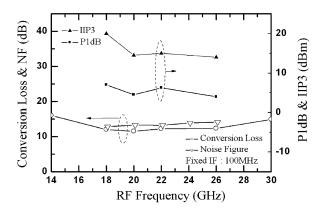

Fig. 6. Measured conversion loss, noise figure,  $IP_{1dB}$  and  $IIP_3$  as a function of the RF frequency at the LO power of 7 dBm.

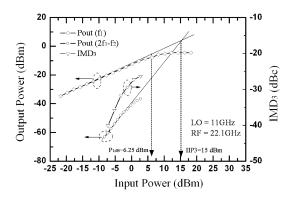

Fig. 7. Measured IP $_{\rm 1dB},$  IIP $_{\rm 3}$  and IMD $_{\rm 3}$  of the 0.13  $\mu\rm m$  CMOS SPRM with the integrated Marchand balun.

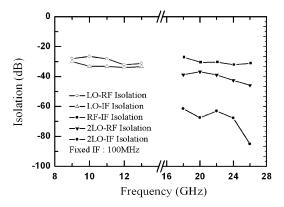

Fig. 8. Measured port-to-port isolations for the 0.13  $\mu m$  CMOS SPRM with the integrated Marchand balun, IF= 100 MHz.

anti-phase modulation, the net effective channel conductance of the SPRM appearing in the IF port is modulated at twice of the LO frequency. After mixing with the RF signal, the in-phase IF signal  $(f_{\rm RF}-2f_{\rm LO})$  is extracted from the IF low pass filter. To reduce conversion loss, the ratio of the channel conductance between the on-state and off-state must be increased by injecting more LO power and biasing the gate voltage near the threshold voltage. As shown in Fig. 2, the simulated channel resistance of the NMOS employed in this design is described as the function of the gate voltage. This NMOS has the minimum  $R_{\rm ds(total)}$  of  $8.2~\Omega$  for the ten-finger device with unit gate width

| Tech.                            |      | RF(GHz)   | CL(dB)  |       | LO(dBm)         | LO-RF(dB) | LO-IF(dB) | IIP3  | Size(mm <sup>2</sup> ) |

|----------------------------------|------|-----------|---------|-------|-----------------|-----------|-----------|-------|------------------------|

| 0.2 um InGaP/InGaAs/GaAs PHEMT   | [2]  | 10-12     | 6.5     | 12    | (Gate Pumping)  | 65        | 37        |       | Hybrid                 |

| 0.15 um AlGaAs/InGaAs/GaAs PHEMT | [3]  | 40-45     | 10      | 7     | (Gate Pumping)  |           |           |       | Hybrid                 |

| 0.15 um InGaAs PHEMT             | [4]  | 85-92     | 4.7 ~10 | 10    | (Gate Pumping)  | 15~25     | 20~30     |       | 1.00x2.00              |

| 0.15 um InGaAs PHEMT             | [5]  | 27.5-28.5 | 11      | 13    | (Gate Pumping)  | 35        | 30        |       | 1.00x2.00              |

| 90 nm CMOS (SOI)                 | [7]  | 30-40     | 4.6     | 7.5   | (Drain Pumping) | 48        | 45        | 2     | 0.50x0.47              |

| 90 nm CMOS (SOI)                 | [8]  | 26.5-30   | 10.3    | 0     | (Gate Pumping)  | 24        | 22        | 12.7  | 0.50x0.32              |

| 90 nm Standard CMOS              | [9]  | 9-31      | 8~11    | 9.7 ( | Source Pumping) | 17        | 22.5      | 3     | 0.90x1.00              |

|                                  |      | 6.5~20    | 12~15   | 3.3   | (Gate Pumping)  | 19        | 37.7      | 7     |                        |

| 0.13 um Standard CMOS This       | Work | 18~26     | 11~12   | 4~8   | (Gate Pumping)  | 30        | 33        | 14~20 | 0.68x0.60              |

$\label{table I} TABLE\ I$  Comparison of the Performances for Pumped Resistive Mixers

of 6  $\mu$ m. The conversion loss can be minimized as the ratio of  $R_{\rm ds(max)}/R_{\rm ds(min)}$  increases. The best dc bias is approximately at 0.3 V for the efficient conversion.

The photograph of the sub-harmonically pumped resistive mixer is shown in Fig. 3. The die size is  $0.68 \times 0.6 \text{ mm}^2$ . The layout is symmetrical to reduce the mismatch, and then better port-to-port isolation can be achieved. The realized size of the Marchand balun is  $478 \ \mu\text{m} \times 250 \ \mu\text{m}$ . The thickness, spacing and width of the spiral metal designed at 11 GHz are  $3.4 \ \mu\text{m}$ ,  $2 \ \mu\text{m}$ , and  $14 \ \mu\text{m}$ , respectively. Notice that wider metal widths can be employed here and thus the metal loss is somewhat small [11].

## III. MEASUREMENT RESULT

Fig. 4 shows the conversion loss as a function of the LO power at the fixed IF frequency of 100 MHz. When the LO power exceeds 4 dBm, the conversion loss reaches the flat minimum region, and stays around 12 dB. The minimum conversion loss of 11.5 dB is under the condition of LO = 10 GHz and  $P_{\rm LO}$  = 7 dBm. The measured return loss at the RF, LO and IF ports is represented in Fig. 5.

The conversion loss, noise figure,  $IP_{1dB}$  and  $IIP_3$  versus the RF frequency are shown in Fig. 6. For RF frequencies from 18 to 26 GHz, the conversion loss is less than 12.5 dB and varies within 0.5 dB at the LO power of 7 dBm. Basically, the noise figure is equal to the conversion loss of the passive component. In our experiment, the noise figure is about the same as the conversion loss as expected. The  $IP_{1dB}$  and  $IIP_3$  within the RF bandwidth are better than 4 and 14 dBm, respectively. Fig. 7 depicts the detailed  $IP_{1dB}$ ,  $IIP_3$ , and  $IMD_3$  at  $f_{RF} = 22.1$  GHz.

The measured port-to-port isolations of the SPRM are shown in Fig. 8. The average LO-RF, LO-IF and RF-IF isolations are about -30 dB, -33 dB, and -30 dB, respectively.

The measured 2LO-RF and 2LO-IF isolations also exceed —40 dB and —60 dB. Table I summarizes the state-of-the-art results of the resistive mixers. When compared with the PHEMT process on the semi-insulating substrate, this work integrates the passive mixer with a Marchand balun on the standard CMOS process without any performance degradation, such as required LO pumping power and conversion loss.

## IV. CONCLUSION

In this letter, a K-band SPRM is demonstrated in standard 0.13  $\mu$ m CMOS technology. A Marchand balun directly on

lossy silicon substrate is employed to generate a balanced LO pumping signal. From the measured results, the passive mixer has the conversion loss of 11–12 dB with 4–8 dBm LO pumping power for the RF bandwidth of 18–26 GHz. Thus, this SPRM with the miniature Marchand balun fabricated by the standard silicon process is suitable for the high-frequency applications.

## REFERENCES

- [1] L. Sheng, J. C. Jensen, and L. E. Larson, "A wide-bandwidth Si/SiGe HBT direct conversion sub-harmonic mixer/downconverter," *IEEE J. Solid-State Circuits*, vol. 35, no. 9, pp. 1329–1337, Sep. 2000.

- [2] H. Zirath, "A subharmonically pumped resistive dual-HEMT-mixer," in *IEEE MTT-S Int. Dig.*, 1991, pp. 875–878.

- [3] H. Zirath, I. Angelov, and N. Rorsman, "A millimeterwave subharmonically pumped resistive mixer based on a heterostructure field effect transistor technology," in *IEEE MTT-S Int. Dig.*, 1992, pp. 599–602.

- [4] Y. J. Hwang, H. Wang, and T. H. Chu, "A W-band Subharmonically Pumped Monolithic GaAs-Based HEMT Gate Mixer," *IEEE Microw. Wireless Compon. Lett.*, vol. 14, no. 7, pp. 313–315, Jul. 2004.

- [5] P. C. Yeh, W. C. Liu, and H. K. Chiou, "Compact 28-GHz subharmonically pumped resistive mixer MMIC using a lumped-element high-pass/Band-pass balun," *IEEE Microw. Wireless Compon. Lett.*, vol. 15, no. 2, pp. 62–64, Feb. 2005.

- [6] S. A. Mass, "A GaAs MESFET Mixer with very low Intermodulation," IEEE Trans. Microw. Theory Tech., vol. 54, no. 12, pp. 4362–4371, Dec. 2006.

- [7] F. Ellinger, L. C. Rodoni, G. Sialm, C. Kromer, G. von Buren, M. L. Schmatz, C. Menolfi, T. Toifl, T. Morf, M. Kossel, and H. Jackel, "30–40-GHz drain-pumped passive-mixer MMIC fabricated on VLSI SOI CMOS technology," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 5, pp. 1382–1391, May 2004.

- [8] F. Ellinger, "26.5–30-GHz resistive mixer in 90-nm VLSI SOI CMOS technology," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 8, pp. 2559–2565, Aug. 2005.

- [9] M. Bao, H. Jacobsson, L. Aspemyr, G. Carchon, and X. Sun, "A 9–31-GHz subharmonic passive mixer in 90-nm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 41, no. 10, pp. 2257–2264, Oct. 2006.

- [10] H. Y. Chang, P. S. Wu, T. W. Huang, H. Wang, C. L. Chang, and J. G. J. Chern, "Design and analysis of CMOS broad-band compact high-linearity modulators for gigabit microwave/mollometer-wave applications," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 1, pp. 20–30, Jan. 2006.

- [11] S. C. Tseng, C. C. Meng, C. H. Chang, C. K. Wu, and G. W. Huang, "Monolithic broadband Gilbert micromixer with an integrated Marchand balun using standard silicon IC process," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 12, pp. 4362–4371, Dec. 2006.

- [12] B. M. Motlagh, S. E. Gunnarsson, M. Ferndahl, and H. Zirath, "Fully integrated 60-GHz single-ended resistive mixer in 90-nm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 16, no. 1, pp. 25–27. Jan. 2006.