# **Enhancement of Charge-Storage Performance in Ni-Silicide** Nanocrystal Devices by Thermal Annealing a Ni–Si–N Thin Film

Wei-Ren Chen, Ting-Chang Chang, b,\*,z Jui-Lung Yeh, and Chun-Yen Chang

<sup>a</sup>Institute of Electronics, National Chiao Tung University, Hsin-Chu 300, Taiwan Department of Physics and Institute of Electro-Optical Engineering, Center for Nanoscience and Nanotechnology, National Sun Yat-set University, Kaohsiung 804, Taiwan

The stored charge characteristics of Ni-silicide nanocrystals embedded in nitride formed by annealing a Ni-Si-N thin film were studied in this paper. We used X-ray photoelectron spectroscopy, leakage current density, and X-ray diffraction to offer chemical material analysis of nanocrystals with surrounding dielectric and the crystallization of nanocrystals for different thermal annealing treatments. Transmission electron microscope analyses revealed nanocrystals embedded in the nitride layer. Nonvolatile Ni-Si nanocrystal memories with 600°C annealing revealed superior electrical characteristics for charge-storage capacity and reliability compared with the memories with 300 and 500°C annealing. In addition, we used energy-band diagrams to explain the significance of surrounding dielectric for reliability.

© 2008 The Electrochemical Society. [DOI: 10.1149/1.2971189] All rights reserved.

Manuscript submitted May 27, 2008; revised manuscript received July 18, 2008. Published September 9, 2008.

In recent years, portable electronic products, such as digital cameras, notebook computers, MP3 walkmans, intelligent IC cards, USB flash storage disks, etc., have been widely applied daily and play important roles in the consumer market. These electronic products are all embedded with flash memory devices. As the demand for flash memory devices grow increasingly, the device density and operation speed of flash memory as well as device reliability have also received much attention. For the development of a nextgeneration nonvolatile memory (NVM) technique, devices should be compatible with the current integrated circuit manufacture process. Therefore, the silicon-oxide-nitride-oxide-semiconductor (SONOS) type and nanocrystals (NCs) memory structures have been proposed and demonstrated to lead to an improvement in reliability compared with conventional NVM because of employing discrete traps served as charge-storage media. <sup>5,6</sup>

In order to overcome the limitations of conventional NVM for the scaling-down process, we proposed memory structures that were combined with SONOS-type and metal NCs to obtain good chargestorage ability and strong coupling with conduction channel. In our work, we used a Ni-Si-N thin film to control the size and distribution of NCs by the internal competition mechanism and studied the stored charge characteristics of Ni-silicide NCs embedded in nitride under different temperature effects. It was found that the crystallization of NCs and the quality of surrounding dielectric were distinct from the different temperature annealing; and thus that the annealing temperature was a key parameter for the charge-storage properties of NVMs.

## Experimental

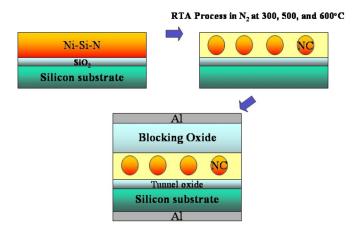

This memory cell was fabricated on a 4 in. p-type silicon (100) wafer with a resistivity of 10  $\Omega$  cm. After a standard clean process and native oxide removing, a 5 nm thick tunnel oxide was thermally grown by a dry oxidation process in an atmospheric-pressure chemical vapor deposition furnace. Afterward, a 10 nm thick nitrogenincorporated Ni<sub>0.3</sub>Si<sub>0.7</sub> layer serving as the charge-trapping layer was deposited by sputtering a Ni<sub>0.3</sub>Si<sub>0.7</sub> commixed target in Ar/N<sub>2</sub> (24/10 sccm denotes cubic centimeter per minute at standard temperature and pressure) environment at room temperature, and the dc sputtering power was set to 80 W (deposition pressure ~7.6 mTorr). Here, we could obtain a Ni–Si–N thin layer by X-ray photoelectron spectroscopy (XPS) analysis (not shown). Then, a 30 nm thick blocking oxide was deposited by plasma-enhanced chemical vapor deposition at 300°C. In this study, before blocking oxide deposition, the charge-trapping layer was annealed at 300°C (sample A), 500°C (sample B), and 600°C (sample C) for 100 s using a rapid thermal annealing system to improve the shape and crystallization of NCs. Finally, Al gate electrodes on the back and front sides of the sample were deposited and patterned to form a metal/oxide/insulator/oxide/silicon (MOIOS) structure. The formation flow of the memory cell structure is shown in Fig. 1. Electrical characteristics, including the capacitance–voltage (C-V) hysteresis, retention, and endurance characteristics were also performed. The C-V characteristics were measured by an HP4284 Precision LCR meter with a high frequency of 1 MHz. In addition, transmission electron microscopy (TEM), XPS, and X-ray diffraction (XRD) were adopted for the microstructure analysis, chemical material analysis, and crystallization of NCs.

#### **Results and Discussion**

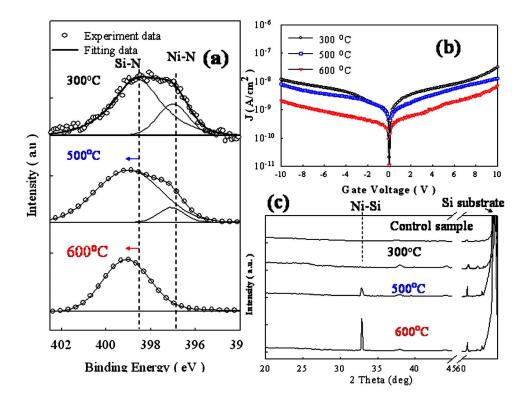

Figure 2 exhibits the material analyses of the charge-trapping layer under the annealing temperature conditions of 300, 500, and 600°C. Figure 2a shows the N 1s core-level spectra with different temperature annealing. Obviously, the spectra are composed of two peaks, SiN (396.8 eV) and Ni-N (398.5 eV), for 300 and 500°C annealing. 8,9 The peak signal of Si–N bonding shifted toward higher binding energy, and the peak signal of Ni-N gradually decayed until it disappeared as the temperature increased. To further ascertain the crystallizations of NCs with different temperature annealing, XRD analyses were executed. As shown in Fig. 2c, the diffraction peak of

Figure 1. (Color online) Formation flow of the MOIOS structure under different annealing temperatures (300, 500, and 600°C).

Electrochemical Society Active Member.

<sup>&</sup>lt;sup>z</sup> E-mail: tcchang@mail.phys.nsysu.edu.tw

**Figure 2.** (Color online) (a) N 1s XPS analysis of NCs (empty circles and straight line indicate experimental and fitting results, respectively). (b) Leakage current density (A/cm²) with gate voltage and (c) XRD analysis of NCs during different thermal annealing temperatures.

32.8° indicates the Ni–Si NCs are formed with an annealing temperature over  $500^{\circ}\text{C}$ . <sup>10</sup> (The control sample is only a structure of Si substrate with tunnel oxide.) From XPS analyses, we considered that the quality of the surrounding dielectric,  $\text{SiN}_{x}$ , had been improved by a reducible reaction of Ni–N during the thermal annealing process. To verify this view point, the leakage current density J (A/cm²) with gate voltage was measured (as shown in Fig. 2b). It was found that the leakage current after  $600^{\circ}\text{C}$  annealing was the lowest under 0 to  $\pm 10$  V sweeping. Moreover, the compound of NCs could be changed from Ni–N to Ni–Si after the annealing process and also affect charge-storage characteristics for the NVM application.

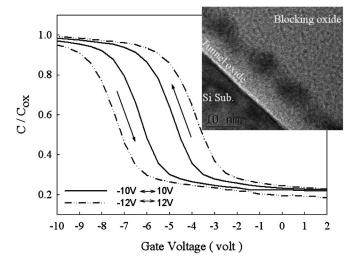

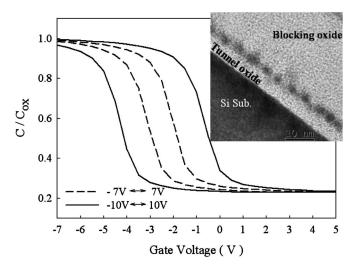

In general, the forward (from accumulation state to inversion state) and reverse C-V hysteresis was measured to investigate the

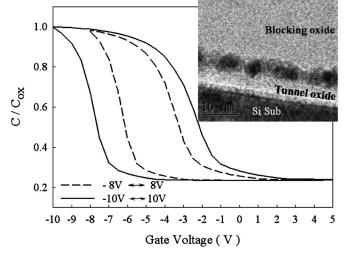

charge-storage abilities of nonvolatile NC memories. Figure 3 presents the memory effect and TEM image (inset) of Ni–N NCs (sample A), and it is clearly observed that memory windows of 1.5 and 3.5 V can be obtained under  $\pm\,10$  and  $\pm\,12$  V operations, respectively. When the annealing temperature increases from 300 to 500°C (sample B) and 600°C (sample C), the memory window raises to 5.0 V for sample B and 4.0 V for sample C under  $\pm\,10$  V sweeping operation. Moreover, these samples also show that the roundness and isolation of NCs are better than for sample A by TEM analyses, as shown in Fig. 4 and 5. These physical phenomena could be contributed by a thermal-enhanced congregation of Ni atoms. According to a previous theoretical model about the probability of an electron escaping from the NC back to the channel, the spherical NCs can reduce the Weinberg impact frequency, which is af-

**Figure 3.** C-V hysteresis and TEM image (inset) of nonvolatile Ni–N NC memories (300°C). The memory window was 1.5 V under  $\pm 10$  V operation

**Figure 4.** C-V hysteresis and TEM image (inset) of nonvolatile Ni–Si NC memories (500°C). The memory window was 5.0 V under  $\pm 10$  V operation

**Figure 5.** C-V hysteresis and TEM image (inset) of nonvolatile Ni–Si NC memories (600°C). The memory window was 4.0 V under  $\pm 10$  V operation

fected by the geometry effect. <sup>11</sup> The more-separated NCs could also restrain the electrons' lateral migration effect under a retention test, because the electrons stored in the NC lift the energy level of the NC conduction band, resulting in the increase of the escaping probability. Therefore, the rotundity and severance of NCs are good for the sub-50 nm gate-length process application.

We further compared charge-storage characteristics of samples A-C such as the memory window, retention, and endurance. The results are listed in Table I. The memory window of sample B is three times larger than that of sample A. Because the resistivity of Ni–Si NCs (14–20  $\mu\Omega$  cm) is smaller than Ni–N NCs (151.7  $\mu\Omega$  cm) and the resistivity is inverse with the density of states, which is a property that affects the number of storage charges, 12 sample B has a superior memory window due to a lower amount of Ni-N NCs (as shown in Fig. 2). Hence, it is believed that the nonvolatile memory capacity was greatly influenced by the crystallizations characteristic of Ni-Si and Ni-N NCs. In addition, the initial memory window was fixed at the same value for the retention and endurance test. The memory window of retention was obtained by comparing the C-V curves from a charged state (write/erase (W/E) state) and the quasi-neutral state, for which we used an extrapolation (between  $1-10^4$  s) to give a long-term predictable result (10 years). Furthermore, the W/E biases for endurance were set at  $V_{\text{G}}$ - $V_{\text{flatband}} = \pm 5 \text{ V for } 0.1 \text{ ms}$  (this condition was enough to define the data information for the current NVMs). Table I clearly indicates that the reliability of nonvolatile Ni-Si NCs memories (sample B and sample C) is better than Ni-N NCs (sample A). According to the

Table I. Comparison table for the memory window retention, and endurance. The initial memory window was fixed at the same value for the retention and endurance test.

|                     | Memory<br>window<br>under<br>± 10 V | window after 10 years (retention: electrons holding ratio) | Memory<br>window<br>after 10 <sup>6</sup> W/E<br>cycles (endurance) |

|---------------------|-------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|

| Sample A<br>(300°C) | 1.5 V                               | 0.5 V (20%)                                                | 1.0 V (degradation 50%)                                             |

| Sample B (500°C)    | 5.0 V                               | 0.7 V (31%)                                                | 2.1 V (degradation 0%)                                              |

| Sample C (600°C)    | 4.0 V                               | 1.1 V (50%)                                                | 2.1 V (degradation 0%)                                              |

**Figure 6.** Energy-band diagrams of (a) Ni–N NCs ( $300^{\circ}$ C), (b) Ni–Si NCs ( $500^{\circ}$ C), and (c) Ni–Si NCs ( $600^{\circ}$ C) embedded in the nitride layer.

above-mentioned material analyses, we concluded that the annealing temperature had a great influence on the properties of NCs, and this factor also significantly affected the memory window.

Here, the conjectural energy-band diagrams were proposed to explain these physical phenomena of charge storage, as shown in Fig. 6. Because the density of traps in the nitride layer decreased as the annealing temperature increased, sample C (600°C) had the least trap density, as shown in Fig. 6c. However, the reduction in trap density resulted in a memory window in sample C that was

lower than that of sample B, because the traps of nitride could provide additional charge-storage nodes. Although the nitride traps can improve the memory window, electrons stored in these shallow traps of nitride easily escape to the substrate. In addition, the nitride traps surrounding the NCs also provide leakage paths for the stored carriers of NCs. Both the above drawbacks cause the retention of samples A and B to be worse than sample C. As shown in Table I, the electron holding ratio of 50% of sample C, estimated for 10 years, is much better than sample B (31%) and A (20%). Moreover, the endurance results reveal that samples B and C had excellent reliability after 106 W/E cycles operation, because the stronger silicon-nitrogen bonding (as shown in Fig. 2a) could suppress the damage during W/E operation. Summarizing the above results, the nonvolatile Ni-Si NC memory after an annealing temperature of 600°C exhibits the best NVM performance, and this device can also be used on a low-temperature substrate (<600°C) for nextgeneration applications.

## Conclusion

In conclusion, the nonvolatile memory characteristics were influenced by the crystallizations of Ni–Si and Ni–N NCs. The nonvolatile Ni–Si NC memory showed better charge storage ability and reliability than nonvolatile Ni–N NCs memory, because Ni–Si NCs have higher density of states and stronger surrounding dielectric than the others. Hence, the MOIOS structure needed a 600°C thermal annealing process to obtain a high-performance nonvolatile NC memory in this work. In addition, the proposed energy-band diagrams could clearly explain the trap density of surrounding dielectric, SiN $_{\rm x}$ , and how it affected the NVM characteristics.

## Acknowledgments

This work was performed at the National Nano Device Laboratory (P-96-1A-062) and was supported by the National Science Council of the Republic of China (Taiwan) under contract no. NSC 96-2221-E-009-202-MY3, no. NSC 96-2120-M-110-001, no. NSC 95-2221-E-009-296-MY2, and no. NSC 96-2112-M-110-013.

National Sun Yat-Sen University assisted in meeting the publication costs of this article.

#### References

- S. Tiwari, F. Rana, K. Chan, H. Hanafi, W. Chan, and D. Buchanan, Tech. Dig. -Int. Electron Devices Meet., 1995, 521.

- W. R. Chen, T. C. Chang, P. T. Liu, P. S. Lin, C. H. Tu, and C. Y. Chang, Appl. Phys. Lett., 90, 112108 (2007).

- 3. J. D. Blauwe, IEEE Trans. Nanotechnol., 1, 72 (2002).

- Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, *IEEE Trans. Electron Devices*, 49, 9 (2002).

- C. H. Lee, S. H. Hur, Y. C. Shin, J. H. Choi, D. G. Park, and K. Kim, Appl. Phys. Lett., 86, 152908 (2005).

- T. C. Chang, P. T. Liu, S. T. Yan, and S. M. Sze, Electrochem. Solid-State Lett., 8, G71 (2005).

- W. R. Chen, T. C. Chang, P. T. Liu, J. L. Yeh, C. H. Tu, J. C. Lou, C. F. Yeh, and C. Y. Chang, Appl. Phys. Lett., 91, 082103 (2007).

- I. Crupi, D. Corso, G. Ammendola, S. Lombardo, C. Gerardi, B. DeSalvo, G. Ghibaudo, E. Rimini, and M. Melanotte, *IEEE Trans. Nanotechnol.*, 2, 4 (2003).

- Y. Wang, Z. W. Fu, X. L. Yue, and Q. Z. Qin, J. Electrochem. Soc., 151, E162 (2004).

- 10. J. F. Liu, H. B. Chen, J. Y. Feng, and J. Zhu, Appl. Phys. Lett., 77, 2177 (2000).

- 11. M. She and T. J. King, IEEE Trans. Electron Devices, 50, 9 (2003).

- N. S. Gajbhiye, R. S. Ningthoujam, and J. Weissmuller, *Phys. Status Solidi A*, 189, 691 (2002).